关于电路的输出阻抗,一般可以用spice中的.tf语句在仿真中加以查看,但.tf仿真一般只有输出阻抗在dc或者说零频下的值,那么要如何来查看输出阻抗的频率响应?

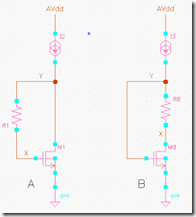

其实还是按照计算输出阻抗的方法,在输出节点加上一个ac=1的交流电流信号,通过ac分析来看此节点的电压,实际就是输出接点的阻抗。我们可以以之前谈到的关于super-source-follower电路为例来做些讨论。

下面左图为super-source-follower的电路,我们通过如下的spice语句定义其激励源(包括直流的输入电压和ac的交流电路)

vin in 0 1.25

iout 0 out ac 1

.ac dec 100 10 10g

这样通过smart-spice的.ac的仿真,可以得到如右边所示的阻抗特性,与之前对super-source-follower的分析一致,高频下反馈环路增益下降导致阻抗的上升,之后应该是寄生电容的影响