贴一下十月份的 JSSC 中的几篇论文

A 9-bit 1.8 GS/s 44 mW Pipelined ADC Using Linearized Open-Loop Amplifiers

对 residue amplifier 采用线性化的开环放大器的结构的考虑

A 12-bit 104 MS/s SAR ADC in 28 nm CMOS for Digitally-Assisted Wireless Transmitters

关于 power-on calibration 对CDAC的实配的校正的方法

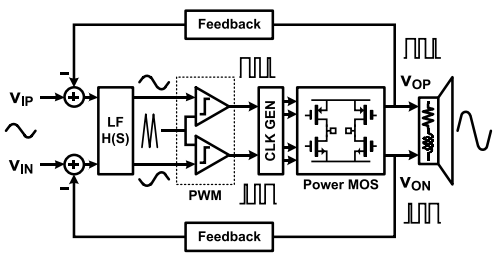

A Load-Adaptive Class-G Headphone Amplifier With Supply-Rejection Bandwidth Enhancement Technique

关于负载阻抗监测的方法,以及采用电源电压选择和class-G开关控制改善效率,并以带宽提升抑制噪声

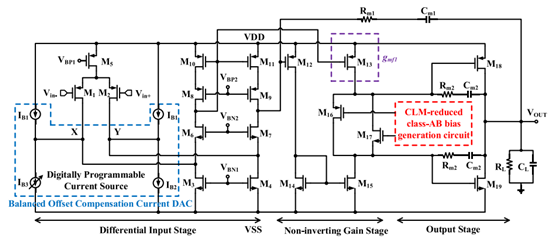

An Analog Front-End for a Multifunction Sensor Employing a Weak-Inversion Biasing Technique With 26 nVrms, 25 aCrms, and 19 fArms Input-Referred Noise

针对运放低频噪声,采用弱反型偏置方法的考量

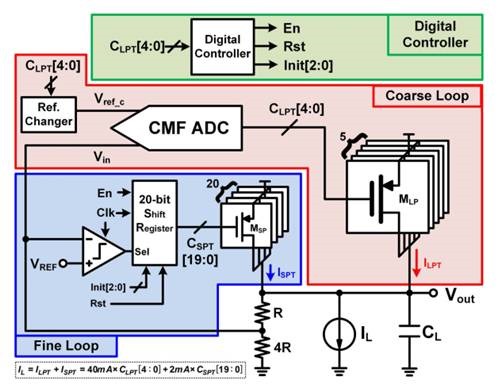

A 1 A, Dual-Inductor 4-Output Buck Converter With 20 MHz/100 MHz Dual-Frequency Switching and Integrated Output Filters in 65 nm CMOS

关于 dual-frequency dual-inductor multi-output buck converter 的设计