这里把 CMOS 中的闩锁效应(latch-up)的来源和一些具体的避免 latch-up 的方法的内容做一些小结.

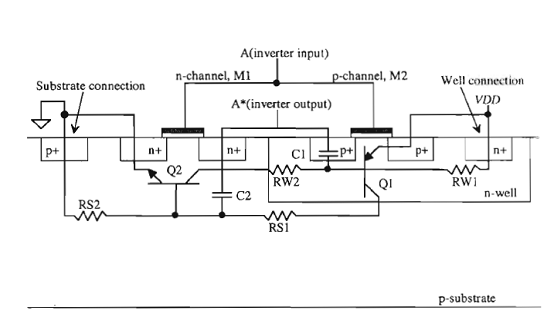

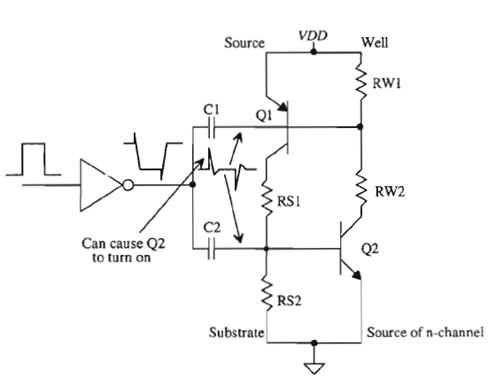

CMOS 中的 latch-up 问题来源于其寄生的 NPN 与 PNP 双极晶体管形成的 PNPN 结构, 具体的闩锁效应产生原理的分析,可以以一对反相器为例(如下图中所示)来说明。

图中 inverter 的 PMOS M2 在阱内形成的纵向双极型晶体管 PNP,NMOS M1 在衬底上形成的横向双极晶体管 NPN,这两个双极晶体管接成一对,可以看到反偏的阱-衬底结是两个晶体管的集电极。

产生 latch-up 的具体原因:

- 芯片一开始工作时 VDD 变化导致 Nwell 和 P-substrate 间寄生电容中产生足够的电流,当 VDD变化率大到一定地步,将会引起 Latch up。

- 当 I/O 的信号变化超出 VDD-GND(VSS)的范围时,有大电流在芯片中产生,也会导致 SCR(silicon-controlled rectifier)的触发。

- ESD 静电加压,可能会从保护电路中引入少量载流子到 well 或 substrate 中,也会引起 SCR 的触发。

- 当很多的驱动器同时动作,负载过大使 power 和 gnd 突然变化,也有可能打开 SCR 的一个 BJT。

- Well 侧面漏电流过大

如何防止 latch-up,具体的方法:

- 在 substrate 上改变金属的掺杂,降低 BJT 的增益

- 避免 source 和 drain 的正向偏压

- 工艺上,在重掺杂的衬底上增加一个轻掺杂的 layer,阻止侧面电流从垂直 BJT 到低阻衬底上的通路

- 使用保护环 Guard-ring: P+ ring 环绕 nmos 并接 GND;N+ ring 环绕 pmos 并接 VDD,一方面可以降低 Rwell 和 Rsub 的阻值,另一方面可阻止载流子到达 BJT 的基极。如果可能,可再增加两圈 ring。

- Substrate contact 和 well contact 应尽量靠近 source 端,以降低 Rwell 和 Rsub 的阻值。

- 使 nmos 尽量靠近 GND, pmos 尽量靠近 VDD, 保持足够的距离在 pmos 和 nmos 之间以降低引发 SCR 的可能

- 除在 I/O 处需采取防 Latch-up 的措施外, 凡接 I/O 的内部 mos 也应圈保护环 guard ring

- I/O 处尽量不使用 pmos (nwell)