之前大致列了下 ESD 的基本机理/测试模型,这里把集成电路工艺中的 ESD 注入的概念列一下(更多详细的内容建议参考台湾交通大学柯明道教授的这个网站):

具体关于ESD implementation的概念

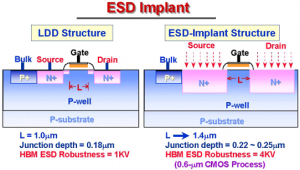

在下图中,示出两种不同的 NMOS 元件结构:

左侧的是 sub-micro process下的标准器件结构,包含有 LDD 的漏(Drain)和源(Source),这里 LDD 是用来减小 MOS 漏端在沟道下的电场强度分布,以克服因热载流子效应 (Hot carrier effect) 所造成的 I-V 特性因长时间使用而发生漂移的问题。

这个 LDD 结构做在 MOS 器件沟道 (channel) 的两端,由于 LDD 的结深 (junction-depth) 较小,等效在漏极和源极的两端形成了两个”尖端”,故而在 LDD 这个尖端结构上,容易发生”尖端放电”现象。

当这种 LDD 器件用于输出级 (output buffer) 时,NMOS 器件就很容易被 ESD 所破坏,即使 MOS 器件在输出设计中拥有很大的尺寸 (W/L),其 ESD 防护能力在 HBM 测试下仍常低于1000伏特。

为了克服因 LDD 结构所带来的 ESD 保护能力下降的问题,在工艺上发展出 ESD-Implant Process: 就是在同一 CMOS 工艺中,做出两种不同的 MOS 器件,一种是给內部电路使用,具有 LDD 结构的 MOS 器件,另一种是给 I/O 用,不具有 LDD 结构的 MOS 器件

具体来说,就是在原先的工艺流程中再加入一层 ESD-Implant 用的 Mask (掩膜),利用此 ESD-Implant Mask 再加上一些额外的工艺步骤,就可在同一工艺中做出不同的 MOS 器件。由于用 ESD-Implant Mask 做出的元件不具有 LDD 的结构,其结构像传统的长沟工艺所做出的元件,故其像早期的 MOS 元件一样,有比较高的 ESD 保护能力。

需要注意的是, 利用 ESD-Implant Process 做出的 MOS 元件有较深的结深, 故其有比较严重的橫向扩散, 导致利用 ESD-Implant Process 做的 MOS 元件不能用太短的沟长.

另外, 用 ESD-Implant Process 做的 MOS 元件与 LDD 结构的 MOS 元件不同, 故需要另行提取元件的 SPICE 参数, 以利电路模拟.

Pingback引用通告: ESD Note-3 | Return To Innocence