最近大致看了下集成电路静电保护(ESD – Electro-Static Discharge)相关的内容,这里简单小结下,要是以后要深入的话,就打算把下面的几本ESD的书再仔细研读一下:

- ‘ Basic ESD and I/O Design ‘ – Sanjay Dabral, Timothy maloney

- ‘ ESD in Silicon Integrated Circuits ‘ – Ajith Amerasekera, Charvaka Duvvury

- ‘ On-Chip ESD Protection for Integrated Circuits: An IC Design Perspective ‘ – Albert Z.H.Wang

另外,在台湾交通大学的这个网站亦有提供关于 ESD 静电防护的很好的学习资料

关于 ESD

ESD 是一种瞬间静电泄放现象,典型的持续时间为~150ns。它所引起的大电流(可至几十安培)和高电压(可达几万伏)的瞬态会导致IC芯片的损坏。

ESD 机制/模型

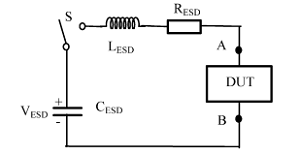

1.Human-body model (HBM)

带电人体接触芯片(的静电泄放)模型

此模型中,串联 RC(100 pF 电容和 1.5K ohm 电阻),也有文献中另外串联上电感(为 7.5uH)

ESD 峰值电流约为 1.3A,上升时间 10~30ns

HBM 是接受最广的 ESD 模型

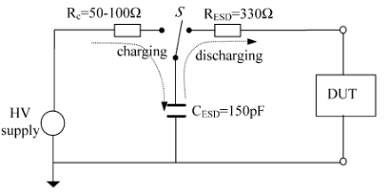

2.Machine model (MM)

带电仪器接触 IC 时的静电泄放模型,等效的 ESD 模型与上图类似;串联 RC(200 pF 电容和小于 1 ohm 电阻),也有串联小于 2.5uH 的电感;峰值电流约为 3.7A,上升时间 15~30ns

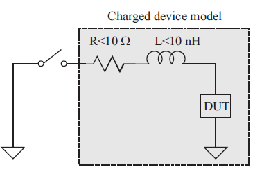

3.Charged-device model (CDM)

CDM 为在 IC 制造过程中芯片自身积累的静电泄放事件的 ESD 模型

具体,其峰值电流大小约为 10A,上升时间约为 1ns

CDM 模型考虑的主要是栅氧的击穿问题(之前的 HBM 和 MM 模型则主要是热失效的问题)

4. 其他 ESD model:

IEC model: international electro-technical commission model

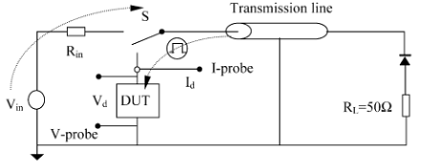

TLP model: transmission line pulse: 主要是利用传输线加上稳定的方波以便于测试

Pingback引用通告: ESD Note-2 | Return To Innocence