在全差分运放的设计中,通常共模反馈的环路会比主运放的级数要多,这时共模反馈环路中多个极点会影响环路的稳定性,这里试着对此问题做些分析.

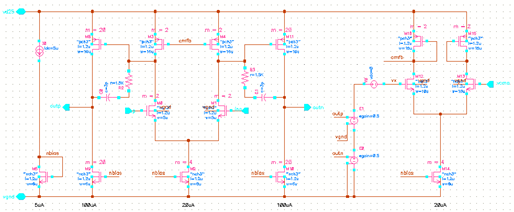

下图是一个简单的两级全差分放大器,其中的cmfb部分利用两个VCVS得到输出信号的共模,再与输入的Vcmo比较得到cmfb的反馈控制信号。

考虑共模反馈环路,其中存在3个极点,包括运放第一级的输出极点、第二级的输出极点以及cmfb节点对应的极点。与分析运放稳定性问题一样,前两者分别为主极点和次主极点,对于第3个极点,由于其阻抗和输出极点一样在1/gm量级(实际上,为消除系统失调,运放输出共源放大的mos管和cmfb的二极管连接的mos管有相同的过驱动电压,其gm按w/l成比例),不能简单的忽略。

实际上,这个cmfb的极点与上图中P管的特征频率ft相关,为此我们需要为其选择一个合适的过驱动电压Vov:首先Vov不能太低,这样才能以保证其ft在足够高的频率,以避免cmfb极点对环路的作用;同时这Vov也不能太高,他必须提供一定的gm/Id,保证运放输出级在电流一定的条件下有足够的gm,从而避免运放输出极点频率的下降。

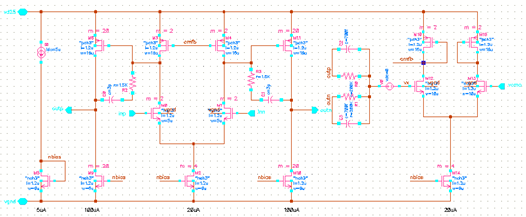

上面是对利用理想VCVS得到输出共模的方式下的一些分析,下面我们看看实际的得到输出共模电路中的问题。

以电阻方式等到输出信号的共模电平是一种常见的方法,如果忽略前面电路的输出阻抗,cm-sense的电阻Rs和之后的共模比较电路的栅节点电容Cx会在共模反馈的环路中引入一个极点。考虑到一般Rs至少要在Rds量级以避免其对运放增益的衰减,这位个极点的位置不会太高,因此必须加以考虑。实际中,可通过在电阻Rs上并联电容Cs来减小这一极点的影响。

在上面的电路中, 通过简单的分析, 可以得到: 引入 Cs 之后, 由 cm-sense 部分引入的零极点为: Po=1/(Rs*(Cs+Cx)), Zo=1/(Rs*Cs), 即在极点之后补了一个零点来抵消其作用. 至于具体的 Cs 的取值, 考虑 Cs 至少与 Cx 比较接近, cmfb 环路才能得到一定的相位裕度, 若进一步考虑零极点对建立时间的影响, 应该将 Cs/Cx 取为一定值以上才能将零极点拉的足够近, 以减小这一零极点对对共模信号建立时间的影响。

第一级输出共模不需要共模反馈吗

博主 有个类似的问题请教一下

1、共模反馈电路在电路中一般就是两级的运放 这个运放的带宽和增益应该怎么限定或者根据什么设置共模电路的基本指标?

2、运放设计好以后,一般会有外围的rc器件组成闭环使用,主环路的稳定性一般实在这种实际的环路中进行仿真的,那共模反馈环路的稳定性是否直接在实际环境中加一个iprob仿真就可以?仿真共模部分的稳定性时候,外围的反馈是否需要断开来防止主环路和共模环路互相嵌套导致错误的仿真结果?

(其实是想请教博主共模环路的指标设置和仿真方法,一直没有学习到确切可靠的设计和仿真方法)

希望博主看到以后能答疑一下 谢谢

请问一下,有结论了吗,我现在也遇到这个问题,在闭环下共模环路增益在某个corner下特别高,并且相位裕度相比反转180°。

版主你好,sansen书模拟集成电路设计精粹(P172)中提到,对应的极点是4/(RX*(CX+CS)),分子4说是电阻并联和电容串联导致的,可是电容也是并联啊,您知道这个是怎么算的吗?

看了一下, 书上说的电容的串联应该指的是共模反馈的两个差分输入管的Cgs, 似乎是认为这里不能用半边电路把差分对的源极认为是小信号地, 而是将另一端的栅,也就是共模输入认为是地.

Ca是并联,然后和(Cgs6)/2并联,结果应该是 2Ca+Cgs6/2吧?

应该是的

那个极点个零点是否写反了

没有错吧

我计算的情况是 前者是零点 后者是极点

我看了没问题,不知道你是怎么算的

看到发的这些文章让我很兴奋,竟有一个对技术这么热衷的网站,以后常来!

不加共模最多是在输入电压不可变上,我是做detla-sigma ADC。

OP负载不好确定导致建立时间过长,对于CMFB,中电容怎么确定问题。SMIC18工艺,参考电流1uA。发现Cgs过大270pf。我看有关文献说CMFB中电容是Cgs几倍。。。糊涂了。这么大?

我的设计的折叠共源共栅的建立时间过长,用共模反馈后是否有改善。我是先设计OP,再打算加入共模反馈

不知道你是怎么不加 cmfb 就能跑的。

如果怀疑 cmfb 问题,可以先用 vcvs 之类搭个理想的共模反馈试试。