6月份的 JSSC, 主要挑了下面的论文:

0.04-mm2 103-dB-A Dynamic Range Second-Order VCO-Based Audio ΣΔ ADC in 0.13-μm CMOS

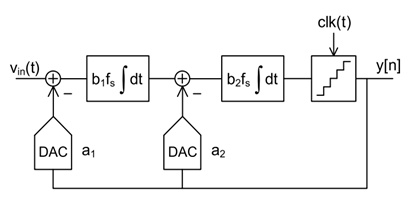

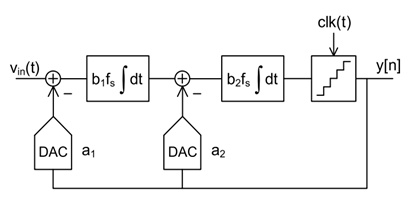

论文主要介绍了用 以 VCO 和几乎全数字方式实现的 SDM ADC, 下图所示分别为基本的 SDM 和利用 VCO 实现的系统:

继续阅读

6月份的 JSSC, 主要挑了下面的论文:

0.04-mm2 103-dB-A Dynamic Range Second-Order VCO-Based Audio ΣΔ ADC in 0.13-μm CMOS

论文主要介绍了用 以 VCO 和几乎全数字方式实现的 SDM ADC, 下图所示分别为基本的 SDM 和利用 VCO 实现的系统:

继续阅读

5月份的 JSSC, 主要挑了下面的论文:

A Nyquist Rate SAR ADC Employing Incremental Sigma Delta DAC Achieving Peak SFDR = 107 dB at 80 kS/s

论文主要介绍了用 Incremental Sigma-Delta DAC 提高 SAR-ADC 精度的方法,如下图所示:

继续关于 Journal of Solid-State Circuits 的论文的纪录, 三月份主要挑了下面的 paper:

下图所示为常见的 CP-PLL 和论文中提到的 SSPD-PLL 的系统框图,以及两种结构中各个电路模块对的系统的相位噪声的贡献的曲线。

二月份的 Journal of Solid-State Circuits 论文, 简单的找了下面这篇记录一下:

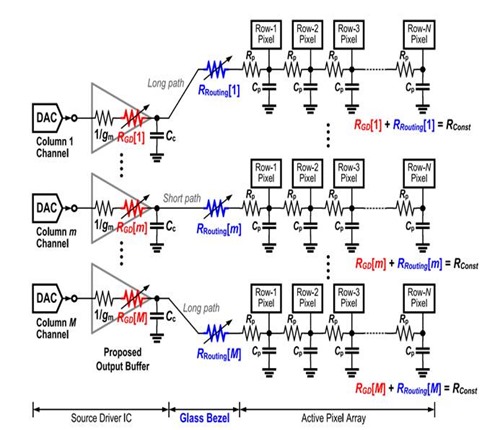

这里主要介绍的是利用在输入差分对加入源极退化电阻来补偿连线电阻的失配问题,基本的原理可见下图.

继续阅读

新一年的开篇,重新出发,这月的 JSSC 主要挑了下面这篇 paper:

这里主要是利用 Current Conveyor 的阻抗变换或者说 buffer 的作用以减少 sensor 中大的寄生电容的影响,同时对相邻的信号做差得到类似差分的结构以避免所谓的 baseline 信号导致的饱和的问题。

基本的系统结构可见下图: