在 IC 设计(如 ADC 电路等)中,有时候要考虑时钟抖动(clock jitter)的影响,通过在设计初期加入带有抖动的时钟模型可以较快的判定其影响。

关于 clock jitter 具体的仿真模型,J.Baker 的混合信号书中提到的方法是利用 spice 中的 SFFM 模型,即单频率频率调制源(Single-Frequency-Frequency-Modulation):

SFFM (Vo Va ...)

也即为如下的函数:

Vsffm(t)=Vo+Va*sin[2*pi*Fc*t+MDI*sin(2*pi*Fs*t)]

在这里,调制率 MDI 决定了峰峰值相位偏移,即 2*MDI=2*pi*dt/Ts=2*pi*dt*Fs, (Ts=1/Fs)

故而,可以简单的认为 peak-peak jitter:dt=MDI/(pi*Fs)

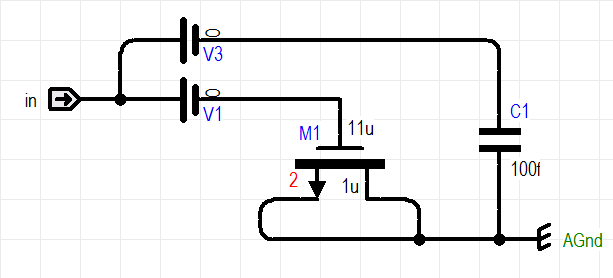

在得到此抖动的正弦信号后,通过理想判决器(比较器)可以将其转换为我们所需的抖动时钟信号

这种方法的问题主要在于:得到的 clock jitter并非随机;J.baker 也在书中也提出通过设置 Fs 与仿真时间来使其更接近实际情况。

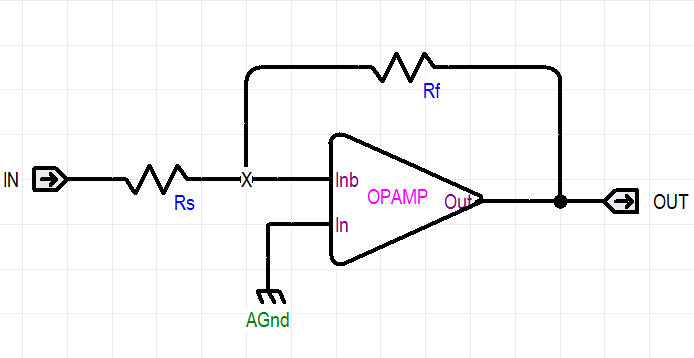

事实上,通过 Verilog-A 工具可以更容易的仿真时钟抖动的影响,一个简单的想法是利用 verilog-A 中的 transition 语句在 delay 中引入随机(利用 $rdist_normal 函数),可参考的部分 Verilog-A 代码如下:

继续阅读