简单的列一下十月的JSSC中的部分内容:

A 15-Gb/s 0.5-mW/Gbps Two-Tap DFE Receiver With Far-End Crosstalk Cancellation

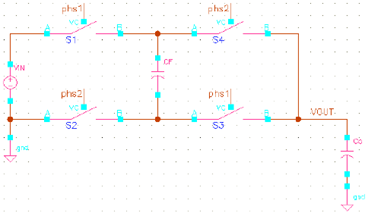

关于开关电容DFE和具体的cross-talk cancel的方法

A 2.4 GHz Fractional-N Frequency Synthesizer With High-OSR ΔΣ Modulator and Nested PLL

在Fractional-N PLL中多级的divider以提高ΔΣ Modulator的过采样率,同时环路中增加PLL以减小噪声混叠