十二月的 Journal of Solid-State Circuits, 找了下面两篇论文简单记录一下:

A 19 nV/√Hz Noise 2-µV Offset 75-µA Capacitive-Gain Amplifier With Switched-Capacitor ADC Driving Capability

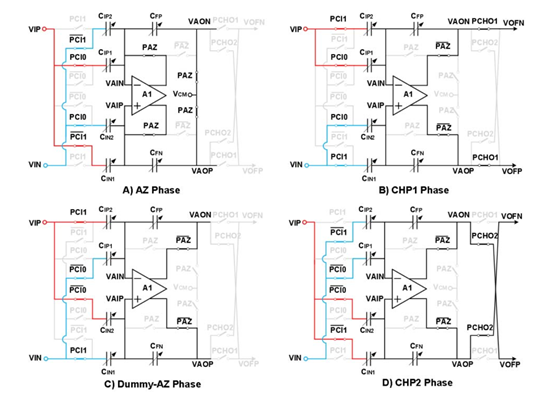

下图所示为其工作的示意,通过将输入电容拆分,并利用 auto-zero 的相位来设置输入共模电压;注意这里存在的 dummy auto-zero 相位使 chopping 的频率大于 auto-zero 的频率,因此不会使得 auto-zero 的噪声折叠回来。