在这里把看到的关于 WPE 和 LOD 效应的内容小结一下

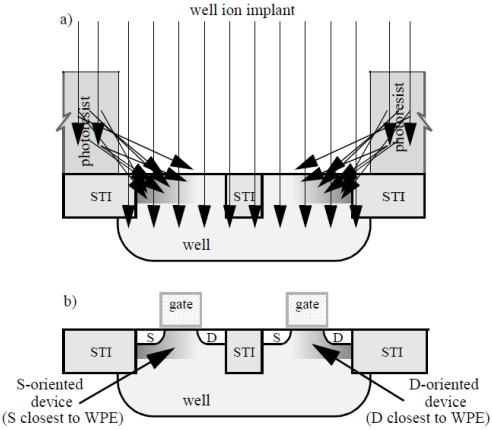

WPE, 也即 Well Proximity Effect, 其原理可以参见下图: 集成电路制造过程中, 在对阱作离子注入时,注入的离子与阱区周围的光刻胶发生溅射而富集在阱的边缘, 因而在水平方向呈现掺杂浓度的非均一性。这会导致阱区中的 MOS 管的阈值或其他电学特性会随着晶体管与阱边缘的距离而发生变化, 这一特性就称为 well proximity effect.

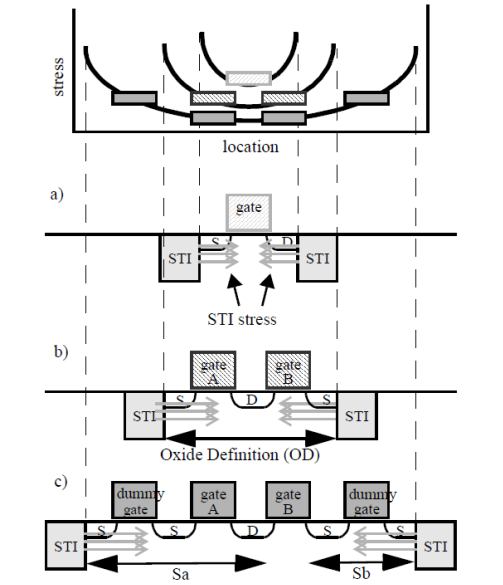

LOD ( Length Of Diffusion) Effect, 也称为 STI stress effect,顾名思义,就是在有源区外的 STI 隔离会对其带来应力作用(如下图中所示),从而影响晶体管的迁移率和阈值电压,因而导致不同的有源区的长度(SA+L+SB)的 MOSFET 的电学特性存在差异。