对于底板采样,一直以来我的理解是为了避免电容底板寄生电容对节点引入的噪声,但在J.Baker的混合信号书中,则是将这种开关的时序选择称为底板采样,这里把里面的内容记录一下。

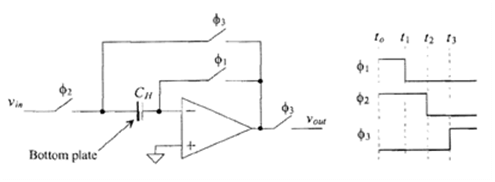

下图所示是基本的S/H电路以及开关的控制时序。

在t0时刻:Φ1和Φ2开关闭合,Φ3开关断开,此时输入信号对电容的底板(图中电容CH的左极板)充电,而电容的右极板因为运放的反馈作用被固定在地电位。

在t1时刻:Φ1开关断开,并且运放在t3-t1时间内(通常认为这段时间很短从而电容上的电荷不发生改变)处于开环工作。由于电容的右极板(顶板)在此前一直处于地电位,因此由Φ1开关断开导致的电荷注入和容性馈通与信号无关。

在在t2时刻,考虑到电容CH右侧为高阻抗(运放开环),理想情况下,Φ2开关断开的电荷将流向其左侧的低阻抗输入电压源,这样电容上的电荷将不受影响。

J.Baker书中正是将这种先断开CH右侧(顶板)开关再断开CH左侧(底板)开关的时序称为底板采样。