咳咳,为了坚持更新,贴一篇以前对全差分运放的共模反馈的小结..

关于全差分放大器

对于全差分放大器,一般可以得到更大的 swing (由于差分信号),同时可以实现对共模干扰、噪声以及偶数阶的非线性的抑制;但其需要有两个匹配的反馈网络,以及共模反馈电路

顺便提一下,对于全差分的折叠共源共栅(folded cascode)放大器,需要注意

- 转换速率(正向与负向)对输入对差分对的尾电流源和 cascode 电流源的考虑

- 非主极点的位置–输入对管的 drain 节点(注意全差分没有镜像极点的问题..),如果考虑 PMOS 输入的结构,将会折叠到 n 管的 cascode,从而减小此节点阻抗,提高此非主极点的频率;但是 P 输入结构亦有其问题,如直流增益和 cmfb 电路的速度(考虑 cmfb 控制的为 cascode 的 pmos 电流源)

关于共模反馈 CMFB

从反馈环路来看,共模的稳定问题来源于闭环的共模增益:由于输入差分对的尾电流源的 local-feedback,通常共模增益较小,导致运放无法控制其输出共模点;通过 CMFB 共模反馈电路,可以提高共模反馈环路的增益,以稳定共模信号。

设计CMFB需考虑补偿以减小环路的稳定时间(settling time)和提高稳定性。

从性能上,我们希望共模反馈的单位增益带宽足够大,但由于 cmfb 的环路相较于差模通路可能有更多高频极点,故此在一定的功耗要求下其 UGB 一般比较难做的高,有书中提到可以将其设计为差模 UGB 的1/3

一般共模反馈的方法是控制放大器的电流源,这里如果是 folded-cascode 的结构,可以考虑用 cmfb 控制 cascode 的电流源而不是输入差分对的电流源—-因其在共模环路中有较少的节点–>更容易补偿等..(另一种考虑是控制尾电流源可能导致共模增益的问题)

另外,对于 cmfb 控制的尾电流源,常见将尾电流源分为两半,其中之一由 cmfb 控制,另一半接恒定偏置电流;这种结构的具体分析可见Gray书12.4.2节的内容,简单来说,single-stage 的 opamp 中控制尾电流源的 cmfb 结构,其 UGB 主要为gmt/CL, 其中 gmt 为尾电流源的跨导,这里拆分尾电流源来减半 cmc 共模控制的部分,这样 UGB 减小,即缩减带宽来提升共模反馈环路的相位裕度,当然 cmfb 的增益相应也减小了;另外恒定偏置部分也可帮助共模电压的初始建立,减小 cmfb 大的扰动。

具体的,共模反馈可以分为连续时间和开关电容两类

连续时间的共模反馈

一般的问题是信号幅度的限制和共模信号干扰,具体的共模反馈的方法:

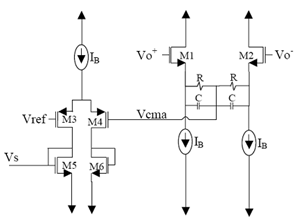

1.电阻分压 resistive-divider (如下左图)

- 电阻和 cm-sense amplifier 的输入电容会引入一个极点,可以通过在电阻上并联电容的方法,引入一个左半平面零点,来减小高频极点的影响

- 另外一个问题,sense resistor 会 load 输出,减小了开环差动增益,考虑通过 voltage buffer 的办法,如source follower,但其也会限制输出的差动摆幅(output swing)

- 关于控制尾电流源和直接 inject 电流的方法的比较(Gray 书)

2. 双差分对或 DDA–differential difference amplifier (如下右图)

- 对输出的 differential – swing 的限制(由于直接取分输出信号到 cmfb 的差分对,为使其工作于饱和区,运放输出 swing 受限于 cmfb 差分对的差模输入范围)

- 详细的大信号分析–>输出差模对输出共模的影响

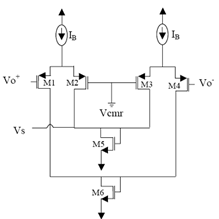

3. 深线性区的 mos 管 transistors in triode region (主要可见 Razavi 书中的分析)

- 对输出 swing 的要求

- 较小的 cmfb 环路增益和带宽

更多关于连续时间的 cmfb 的结构的比较,除了几本教科书的内容,也可以参考:

Duque-Carrillo, J.F.; Continuous-time common-mode feedback networks for fully-differential amplifiers: a comparative study; Circuits and Systems, 1993., ISCAS ’93

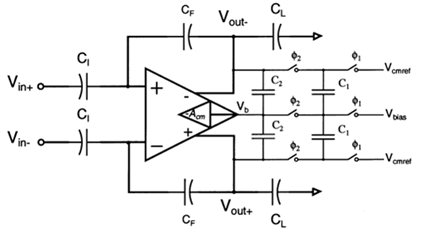

关于开关电容 cmfb

SC-CMFB 结构,一般常用在开关电容电路中,对比连续时间的 CMFB 电路,他支持更大的信号摆幅,同时减小了对输出 swing 的限制,也没有阻性的负载效应;但需要两相非交叠时钟,同时会因非线性时钟馈通注入噪声。开关电容 cmfb 一般结构可见下图,简单来说可以认为电路通过 C2 取得输出信号共模,并用 C1 给其以 DC 点(settle 到 Vcmref-Vbias 的电压)。

一般的开关电容 cmfb:C1 应在 C2 大小的 1/4 到 1/10 之间(Ken Martin),但是也有其他论文谈到不同的选择方法,如:

Ojas Choksi, L. Richard Carley: Analysis of Switched-Capacitor Common-Mode Feedback Circuit, IEEE Transactions on Circuits and Systems—II: Analog and Digital Signal Processing, Vol. 50, No. 12, DEC 2003中具体关于电容大小和开关非理想性的介绍

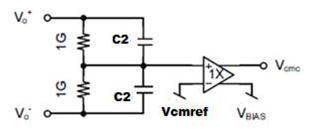

对于 SC-CMFB 的仿真, 与开关电容电路类似, 主要是 pss –> pac 的方法(当然另外也有提到先做瞬态 .tran 分析,再利用 ‘prevoppt’ 取 settle 后 op 点做 ac 分析的方法);一般可以参考的是 Designer’s Guide 上的 ‘Simulating switched-capacitor filters with SpectreRF’ 的这篇论文;如果主要是对差模信号的分析,也可将开关电容的共模反馈电路用连续时间的近似模型代替,如下图

你好,请问C2的具体大小取值怎么来确定?

大小使其对寄生等的非理想不明显同时不增加很多负载

也就是意味着这个电容大小需要根据实际layout的寄生来确定?

大概估一下,还有其他像电荷注入之类

OK,明白,多谢前辈

楼主你好,请问C1应在C2大小的1/4到1/10之间(Ken Martin) 是在kenmartin 哪本书里面找到的呢?在我自己的电路中,ken martin 的取值让transient波形很好,甚至去更大的比例,失真更小。 我有kenmartin的书,我想看看理论的推导,楼主能帮忙吗?谢谢!

刚才打错字了,是哪一章节的?

第六章里面讲共模反馈的部分

谢谢哈,我已经读完了,不过ken martin没有太多推导过程,结论倒是可以用。

我有个疑问,共模反馈能不能提高共模抑制比?Gray的书上说可以降低共模增益,那是不是就提高了CMRR呢?

应该是有帮助的

不一定,也许还减小了CMRR,比如负载电流源两个管子尺寸mismath,CMFB调负载电流源那种,这样CMFB的环路增益会放大两个管子的mismatch效应,CMRR下降。

一定要坚持下去

你好,请问其中的Vbias是什么作用的呢,值如何选取呢?论文中都没有提到~谢谢

看上面最后模型的图示,vbias就是一个直流偏置,当输出共模等于vcmref时,vcmc等于vbias

全差分的折叠共源共栅(folded cascode)放大器转换速率(正向与负向)对输入对差分对的尾电流源和cascode电流源的考虑能否详细说说,感谢!

当时写的时候应该是看的 Ken Martin 书上的一些内容,你可以自己找找看

3Q

你好,想请教一个关于共模反馈的问题 全差分的放大器需要有共模反馈来稳定共模输出点 对于一个单端输入单端输出的 简单CS电路(PMOS电流镜为负载)为什么就不需要共模反馈呢?

对单端的放大器,电压完全可以通过反馈来确定,自然不要什么cmfb了