关于电路的输出阻抗,一般可以用spice中的.tf语句在仿真中加以查看,但.tf仿真一般只有输出阻抗在dc或者说零频下的值,那么要如何来查看输出阻抗的频率响应?

其实还是按照计算输出阻抗的方法,在输出节点加上一个ac=1的交流电流信号,通过ac分析来看此节点的电压,实际就是输出接点的阻抗。我们可以以之前谈到的关于super-source-follower电路为例来做些讨论。

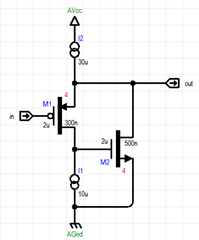

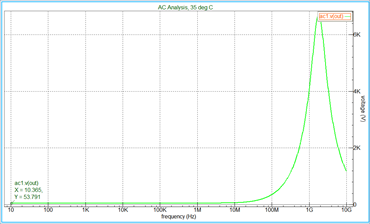

下面左图为super-source-follower的电路,我们通过如下的spice语句定义其激励源(包括直流的输入电压和ac的交流电路)

vin in 0 1.25

iout 0 out ac 1

.ac dec 100 10 10g

这样通过smart-spice的.ac的仿真,可以得到如右边所示的阻抗特性,与之前对super-source-follower的分析一致,高频下反馈环路增益下降导致阻抗的上升,之后应该是寄生电容的影响

另一个例子,可以考虑一下单个mos管的输出阻抗的问题:

对此可以像之前关于单管输出阻抗(或Early电压)的仿真一样,只要看mos管的rds或gds就可以,但同样只有dc下的值。

这里我们同样可以按上图的方法来仿真,但是一般我们只希望仿真mosfet自身的输出阻抗,故此需将其输出接到电流源(因理想电流源的输出阻抗为无限大,不会影响输出节点的阻抗)。这样直接接电流源的接法带来的问题是如何来设定其Vgs的电压偏置,因为Vgs偏压和偏置电流源同时定义MOS管的Ids,可能导致MOS管偏离合适的工作状态。

一个简单的想法是利用电流镜,通过二级管连接的mos管来得到合适的Vgs偏压,但是这样的结构要求两个管子的Vds相同以满足所接的电流源大小相等的条件,因此输出管的阻抗只是对于Vds=Vgs的状态。但是,更多的情况要求我们来查看mos管在不同的Vds偏压下的工作状况(这里就是其输出阻抗)。

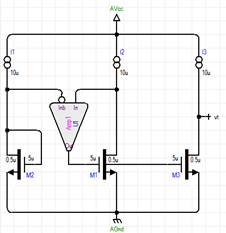

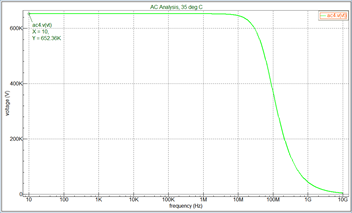

对这一问题,可以考虑利用反馈(以及类似replica bias)的方法,如下面左图所示:通过一个理想放大器,设定其Vds让mos管工作于合适的状态,并以此提供合适的Vgs偏压(图中的二极管连结的M2管提供合适的Vds,我们亦可以换成单纯的电压源,通过设定其大小,来查看输出管在不同Vds(对应的状态下)的输出阻抗的变化);以下图的设定,按前述的仿真输出阻抗的方法,可以得到右图的输出阻抗的特性.

上面谈的主要是在输出点注入 ac 电流源引起的问题,如果考虑是用 ac 电压源(串接在 dc 电压源,或直接赋予其 ac 和 dc 值)来仿真的话(相应的其得到的为输出的导纳),就没有这类问题,就不多说了。

这个是相对频率的解释,可不可以用不同Vgs对应一个ids ,这时候输出阻抗应该也不一样吧,

这个方法真不错,还一直在想怎么处理这个问题呢,学习了,谢谢。电路图也很漂亮,请问是用什么软件画的?