继续之前关于新工艺下的仿真内容的介绍.

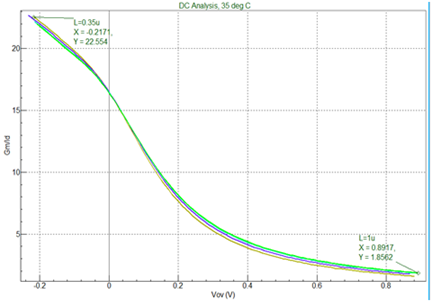

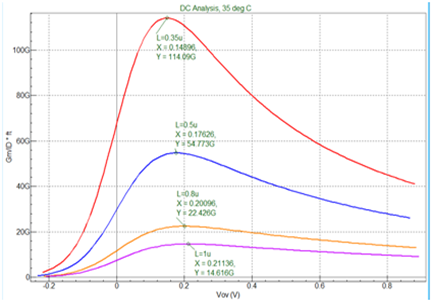

一般在集成电路设计时,对 MOSFET 的过驱动电压 Vov 的选取通常以 150mV~200mV 和 500mV 为分界点(具体可以参见 Willy.Sansen 的 ‘Analog Design Essential’ 一书中相关的分析),当然也可通过 gm/id 曲线来寻找合适的 Vov 电压(关于 gm/id 的设计方法的具体介绍可参见 Stanford 的 EE214 课程文档的说明),个人通常以 Gm/Id*ft 曲线的峰值对应的 Vov 作为一般电路设计中迭代优化的初始点。

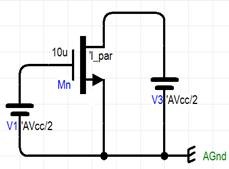

关于 Gm/Id 系列曲线的具体仿真电路,考虑其与之前介绍过的 MOS 管本征增益和特征频率的仿真方法相类似,基本上也是直流扫描的方法来实现的.

具体的仿真电路和对应的仿真脚本如下:

***Smartspice 仿真脚本***

.dc v1 0.3 1.5 0.01

.let vov_n=@Mn[Vgs]-@Mn[Vth]

.let ft_n=1/2/3.14*@Mn[gm]/@Mn[cgtot]

.let gm_id_n=@Mn[gm]/@Mn[id]

.let gm_id_ft_n='gm_id_n*ft_n'

可以分别得到如下图相应的 gm/id 和 gm/id * ft 的曲线: