这里谈一下关于集成电路中的 MOSFET 的输出电阻 Rout 和漏源电压 Vds 电压的问题。

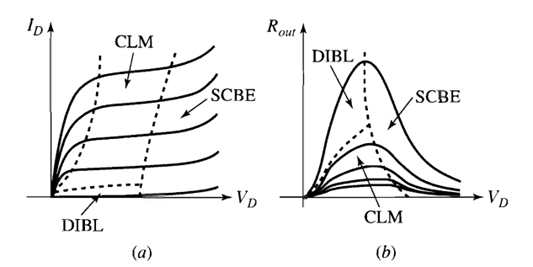

下图所示为 MOSFET 的电流 ID 和输出电阻 Rout 随端电压 VD 变化的曲线

可以看到通常 VD 变化影响 ID 和 Rout 的原因主要是来源于三个因素,分别是: CLM (Channel Length Modulation)- 沟长调制效应;DIBL (Drain Induced Barrier Lowering)- 漏极导致势垒降低; SCBE (Substrate Current induced Body Effect)- 衬底电流导致的体效应。

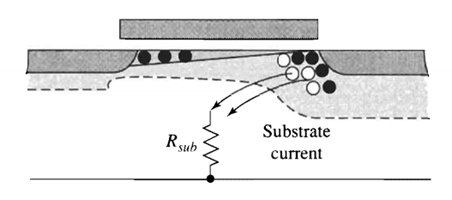

这些效应都会使得 ID 随着 VD 的增大而增大,但对于输出电阻,Rout 会随着 VD 的增大先增大,当VD 增大到一定程度时,Rout 随着 VD 的增大而减小。这主要是因为如 CLM (沟长调制)效应为主导时,其对应的输出电阻 Rout 正比于 VDS (具体的推导可见 《Device Electronics for Integrated Circuits》 一书),但当 VDS 继续增加,由热载流子导致的衬底电流会流过 MOSFET 的体区(如下图所示),并在这一阻性的衬底上产生压降(进一步可能使沟道下的中性区发生正偏),导致所谓的反向体效应,因此电流 ID 显著增大,输出电阻ID 减小。

由于输出电阻 Rout 会随着 VDS 的变化出现一个峰值,因此对 VDS 的选择必须加以注意,除了针对具体集成电路工艺的仿真外,一般也可以粗略考虑将 VDS 选取为1.5倍到3倍的 VOV 。