关于 PLL 相位域分析,有很多书中都有介绍,这里做一些小结

下面电路是利用 Cadence 中的基本元件搭建的 PLL 相位域模型

具体来说,这里的 PFD+CP 利用 VCCS 实现, LPF 直接电阻电容搭建, VCO 利用 VCCS 对单位电容充电实现频率到相位的积分,DIV 利用 VCVS 实现.

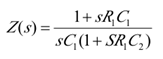

可以看到 LPF 提供的阻抗为:

考虑到 C1>>C2, 可以近似得到:

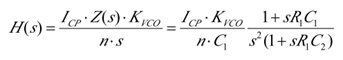

这样可以得到 PLL 相位域的环路传输函数

可以看到系统在原点上有2个极点,另外有一个零点

和一个极点

通常的分析认为相位裕度取得最大值的条件为

这里 ωT 为环路传函的单位增益带宽,而 γ2=ωp/ωz=C1/C2

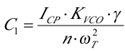

考虑 |H(ωT)|=1, 可以得到

故此在定下 Icp,Kvco 和 n 之后,基本的 LPF 参数都可以通过 ωT 和 γ 来确定。

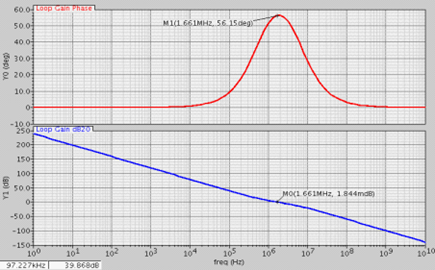

对于 ωT,有论文提及其通常为 PLL 闭环 3dB 带宽的1/1.3, 实际中也可取为1/1.4~1/1.5,通过选择 PLL 的闭环带宽(例如1/10的参考频率以满足连续时间近似)之后,就可相应的确定 ωT; 对于 γ ,他确定了能得到的最大相位裕度,取值为3,4,5时对应的相位裕度分别约为53,62,67。

代入设计的各个参量如 Icp, LPF 的 r1, c1/c2, Kvco, n(div)之后,对之前的相位域模型做 stb 分析,就可得到 PLL 的相位裕度,以判断其稳定性。

我后来发现,这个大家都在采用的相位域模型其实存在缺陷,不是不对,是存在缺陷。

简单的说,pll的refclk上如果有一个扰动,而这个扰动频率与ref 同频,也就是sin(2*pi*fref*t+ Asin(2*pi(fref*t))

扰动量是 Asin(2*pi(fref*t) ,

这个clk 每次上升过零时,其实都看不到这个扰动,因为扰动与clk同频了。

这样这个扰动在输出应该是看不到的,这个可以通过仿真验证。

然而这个s domain的模型,是描述不了这个过程的。原因是s domain无法对pdf输出建模。当把pdf输出 近似等效成 冲击强度为相位差值的冲击序列时,这个东西才能描述清晰。

pll的实际模型,其实并不是书上 s domain近似那么简单。。。

哈喽,作者,你好,请问从这里开始的推导

–>可以看到系统在原点上有2个极点,另外有一个零点。

–>考虑 |H(ωT)|=1, 可以得到

看不懂,可以说明一下吗?谢谢。。

就是用环路增益=1的条件来算参数

想问一下,相位裕度达到最大值时一定在环路带宽的地方吗?

这是通过选择带宽和零极点的位置得到的,放在几何平均值上,书上有推导的

请问PFD/CP传输函数Icp/2pi中的2pi为什么可以去掉?

这里 Icp 的 2pi 和 VCO 的 2pi 约掉了, 也可以都加上