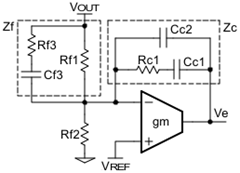

在 voltage mode 的 DC-DC 中,由于功率级中的电感和电容会在环路中引入一对极点,从而会导致环路相位的裕度的问题。为保持环路的稳定,通常的方法是在环路中加上 Type-III 补偿。

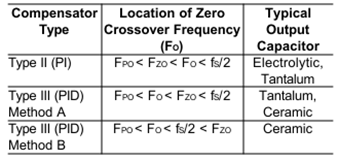

具体的 type-III 补偿的计算或者说补偿电路中的零极点的设置,很多论文中都有不同的方法,这里主要参考的是这篇文章中具体通过 ESR 零点位置来选择两种不同零点位置设置的计算方法。

具体的计算 voltage-mode buck 变换器 Type III 补偿的 matlab 脚本如下:

% calculate the type III compensation network for voltage mode buck converter

%

% -------------------Cc2-----|

% | | |

% | | \ |--Rc1--Cc1---|

% ---------Rf1---------| \ |

% | | | \ _______________|____

% |--Rf3--Cf3--| | /

% | /

% | /

% Rf1>>Rf3, Cc1>>Cc2

%

clc;

clear;

% setting the main parameters of the buck converter

vin=5; % 3.3v or 5v input voltage

vo=1.2; % 1.2v output voltage

d=vo/vin; % the duty cycle in ccm

fs=3e5; % the switching frequency (Hz)

imax=0.5; % the max load current (A)

L=22e-6; % the inductance in the LC filter

C=47e-6; % the capacitance in the LC filter

ESR=0.07; % the esr of C

vm=1.25; % the peak-peak value of the sawtooth wave

delt_I=(vin-vo)/L*d/fs; % the peak-to-peak current ripple (A)

R=vo/(0.5*delt_I); % the equivalent load resistance at the CCM/DCM boundary

%R=1e6;

% calculate the loop-gain without the compensation

s=tf('s');

H1=(vin/vm)*(1+s*ESR*C)/(1+s*(L/R+ESR*C)+s^2*L*C);

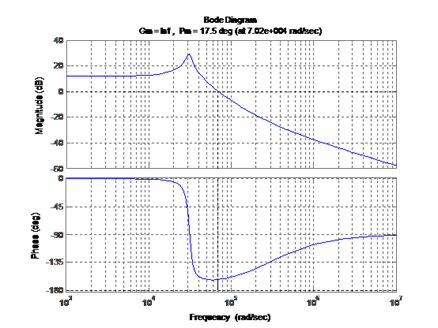

figure(1);

margin(H1);

grid on;

% calculate the pole/zero of the power-stage

fc=0.1*fs; % the cross over frequency

fesr=1/2/pi/ESR/C; % the ESR zero

fpo=1/2/pi/(sqrt(L*C)); % the LC corner frequency

% choose method 1 or 2 based on the fesr

if fesr < 0.5*fs

method=1; % calculate the pole/zero based on method 1

fz1=0.75*fpo;

fz2=1*fpo;

fp2=1*fesr;

fp3=0.5*fs;

else

method=2; % calculate the pole/zero based on method 2

theta=60; % the boosted phase

%k=(1+sind(theta))/(1-sind(theta));

k=(tand(theta/2+45))^2;

fz2=fc/sqrt(k);

fp2=fc*sqrt(k);

fz1=0.5*min(fz2,fpo);

fp3=0.5*fs;

end

% calculate the R/C of the compensation network

Rc1=1.0e5; % choose 100k as a start point

Cf3=(2*pi*fc*L*C/Rc1)*(vm/vin);

Cc1=1/(2*pi*fz1*Rc1);

Cc2=1/(2*pi*fp3*Rc1);

Rf3=1/(2*pi*fp2*Cf3);

Rf1=1/(2*pi*fz2*Cf3)-Rf3;

%% calculate the loop-gain with the compensation

Gc=(1+s*Rc1*Cc1)*(1+s*(Rf1+Rf3)*Cf3)/Rf1/(Cc1+Cc2)/s/(1+s*Rc1*Cc1*Cc2/(Cc1+Cc2))/(1+s*Rf3*Cf3);

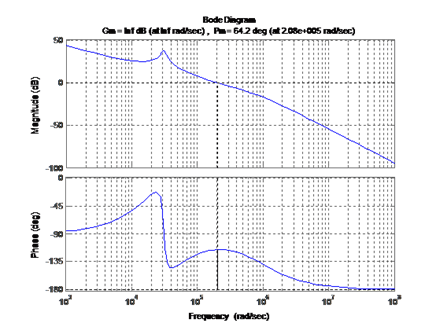

H2=H1*Gc;

[Gm,Pm,Wg,Wp] = margin(H2);

figure(2);

margin(H2);

grid on;

fprintf(1,'Type III compensation, method %g. \n', method);

fprintf(1,'Phase Margin= %g deg @ %gk Hz\n', Pm,Wp/2/pi/1e3);

fprintf(1,'calculated R/C of the compensation network: \n ');

fprintf(1,'Rf1=%gk ohm\n Rf3=%gk ohm\n Cf3=%gpF\n Rc1=%gk ohm\n Cc1=%gpF\n Cc2=%gpF\n', Rf1*1e-3, Rf3*1e-3,Cf3*1e12, Rc1*1e-3, Cc1*1e12, Cc2*1e12);可以看到补偿前后的环路特性

您好,请问第26行的vm=1.25具体是指哪一个电压呢,看了注释还是不太清楚,想请教一下。

请问第26行的vm=1.25具体是指哪一个电压呢,看了注释还是不太懂,想请教一下。

楼主能不能指导下在cadence里如何看补偿部分误差放大器的相位变化,不知道如何设置信号源

放在环路里用stb之类看 loop gain/phase

k=(tand(theta/2+45))^2; 这个计算方法是怎么来的?

参考的 Onsemi 的文章: A General Approach for Optimizing Dynamic Response for Buck Converter

感谢您的回复

基于以上的文献以及算法,我还有几个问题,想请教一下

1 这种电压控制的type 3 补偿,文献A General Approach for Optimizing Dynamic Response for Buck Converter提到的是跨导放大器。那么这种算法对于运算放大器是否同样适用?

2 现在的一些电源芯片例如英飞凌以及英特矽尔,可以同时提供电压控制以及电流控制方式(例如ISL6306 ),对于电流控制的这种算法,例如一般的Peak Current Control 不知道您有什么见解?

3 IR3567B 提供一种数字补偿补偿的方式,通过将S函数转换为Z函数,那么这里涉及到数字滤波器的设计么?

其实很久没做这个方向的工作了.

1. OTA 和 OPAMP 就是输出阻抗的差别,你就用压控电流源和压控电压源放到补偿电路里看看得到的传递函数是不是一样就知道了。

2. 电流模式控制也是算很成熟的东西,没什么见解,应该很多 DC-DC 的书或者论文都有讲的。

3. 还没有用数字方式实现过电源控制环路的补偿,不是很了解。