之前断更有大半年了,中间也收一些朋友的留言询问,考虑还是尽量坚持吧,最近慢慢把之前的内容给补上。

2021年8月份的 JSSC,主要看了下面的论文:

An 8-bit 10-GHz 21-mW Time-Interleaved SAR ADC With Grouped DAC Capacitors and Dual-Path Bootstrapped Switch

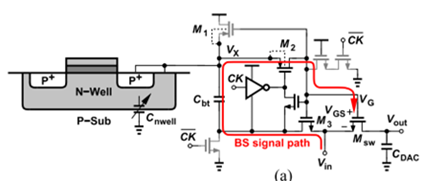

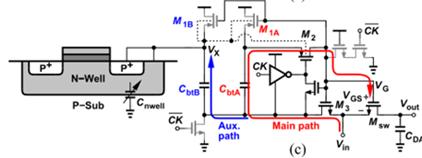

主要是其中的 高速的 bootstrap 开关,采用了 dual-path 的结构,将非线性的寄生电容和关键信号分开,从而提升了系统的SFDR,具体可见下图。

一晃竟然过去了十多年。还记得第一次看到大大的文章是大约十年前,好一个 “事如春梦了无痕,谁与记浮生”。 浮生尚且有六记,希望大侠的更新有无数记。

看到这个dual-path的思路,和我为一个高速timing-interlived ADC 做的一个input buffer 很像。 buffer 用了一个四端都浮动的source-follower, 也是用了dual-path,用辅助path 降低body 的影响, 提升主通路的线性度。

欢迎老师回归,一切安好就好,继续学习