六月的 Journal of Solid-State Circuits, 找了下面这篇论文记录一下:

A 134-μW 99.4-dB SNDR Audio Continuous-Time Delta-Sigma Modulator With Chopped Negative-R and Tri-Level FIR-DAC

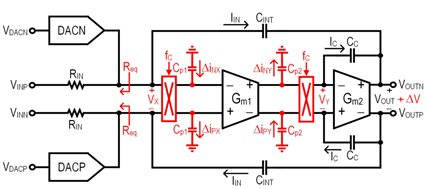

下图为连续时间 SDM 中的包含反馈的第一个积分器的示意图,对积分器的运放的第一级 GM1 加入了 chopping 来改善 1/f noise。这里的问题主要是考虑到积分器中的运放有限增益和带宽,chopping 会将带外的量化噪声采样到寄生电容上,并通过积分电容导致输出误差。

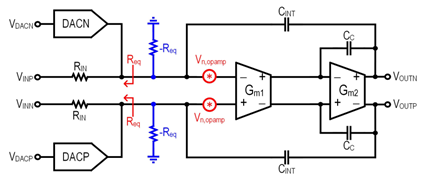

为此,论文采用了下面的负阻的方式,通过在运放的输入加入与积分器输入相同的负阻抗,可以使得积分器中运放输入的等效噪声到积分器输入的等效噪声的传递函数具有高通的特性,从而抑制了积分器的噪声,同时负阻抗也能补偿积分器中运放有限增益和带宽的问题。

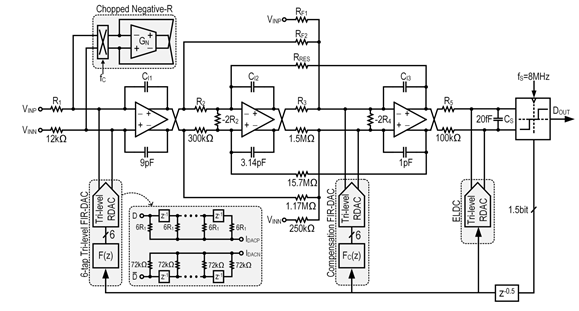

对于负阻部分自身的1/f 噪声,则考虑通过 chopper 的方式来抑制,下图所示为整个连续时间 SDM 的结构示意,这里1.5bit + FIR DAC 的反馈除了等效的多-bit 反馈的考虑,也利用 FIR 的 notch 来进一步抑制 chopping 带来的量化噪声混叠的影响。

偶然看到这里,这个电路。。。很多年前,我给北大做过一个加速度传感器的电路。。。和第一张图几乎完全一样的。区别在于把DACN/P换成电容,Rin/Rip换成传感器本身电容。这个环路很棒,噪声很好。我当时设计chopper的时候,开关泄露的交叠时间没有控制好,然后温飘就飞了,其它性能都很好。