三月的 JSSC,主要看了下面的论文:

A 77.1-dB-SNDR 6.25-MHz-BW Pipeline SAR ADC With Enhanced Interstage Gain Error Shaping and Quantization Noise Shaping

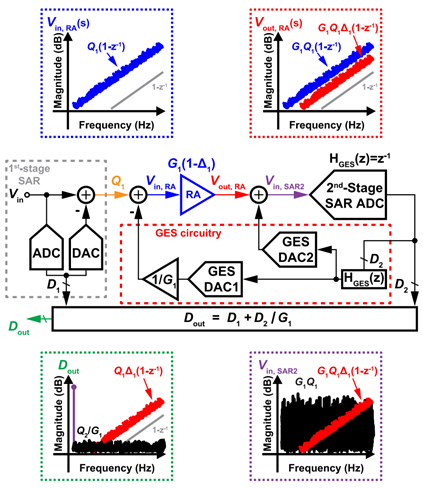

论文主要是考虑 pipeline sar adc 中的 interstage gain error 带来的 quantization leakage error 的问题。下图所示为加入了 gain error shaping 环路的两级 pileline sar adc,注意这里通过 GES filter 和两个 DAC 来对误差信号实现的 high-pass 的方法。

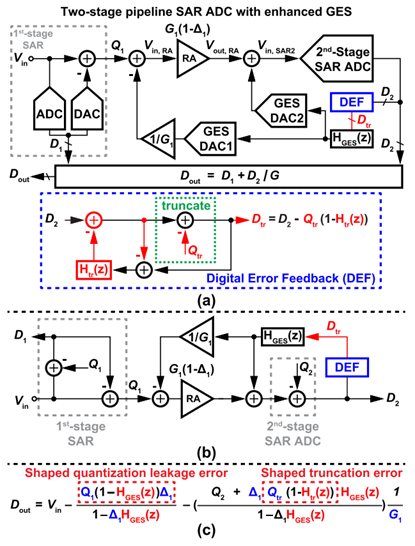

这里的主要问题在于 1/G1 的系数的实现,要求对应电容有很大比值,为减轻这一要求,常见的方法是减小 GES DAC 的位数,但这会带来额外的 truncation error。对此,论文提出了 digital error feedback 的方式,如下图所示,同样对truncation error 做了 shaping。