十一月的 JSSC,主要看了下面的论文:

A Multi-Loop Slew-Rate-Enhanced NMOS LDO Handling 1-A-Load-Current Step With Fast Transient for 5G Applications

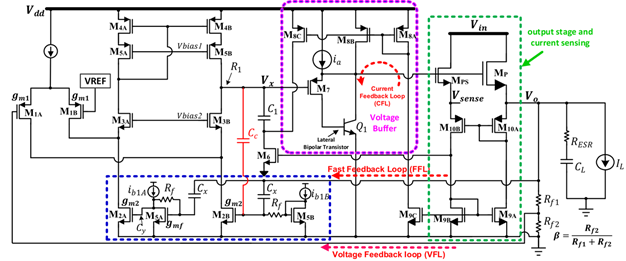

论文主要是关于大电流负载下的 LDO 的设计,包括大负载带来的直流增益 和瞬态响应的问题。这里首先采用了 NMOS LDO 的结构,由于其 source follower 方式的低输出阻抗,增益对负载电流较不敏感,从而在大的负载范围下有更好的 line / load regulation。此外,电路中主要是采用了 multi-loop 的方式,来改善系统的瞬态响应。

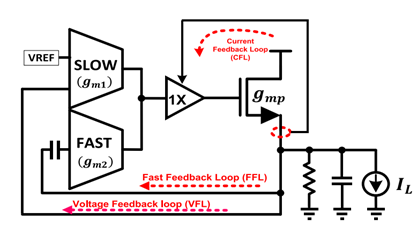

如上图中所示,电路中包含三个控制环路:VFL(voltage feedback loop)是常见的反馈通路,决定了 DC Gain,包括输出的分压电阻,EA,buffer 和 NMOS FET;FFL(fast feedback loop)主要用来扩展环路的带宽,利用类似微分器的方式得到对输出电压的 spike 的响应;CFL(current feedback loop)主要是为了在大负载时做出更快的响应。

论文的电路实现可见下图,可以注意其中 FFL 和 CFL 的具体结构。