继续 5 月份的 JSSC,主要看了下面的论文:

A Dynamic Power Reduction Technique for Incremental ΔΣ Modulators

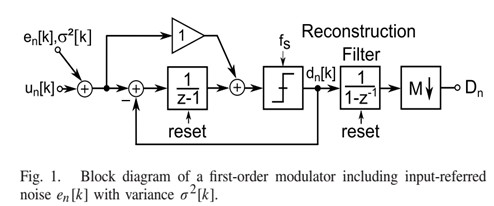

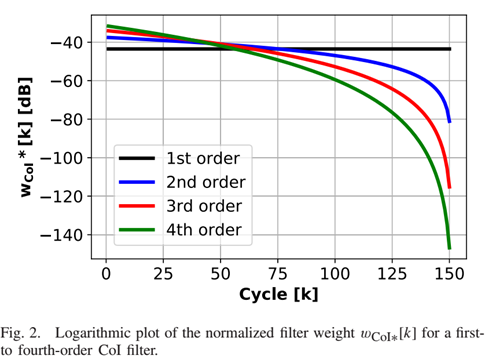

论文主要是通过对 Incremental ΔΣ Modulators (如下图1)中的数字滤波部分的分析,考虑其对每时钟周期 k 的输出 dn[k] 的权重与 k 的 关系,如下图2.

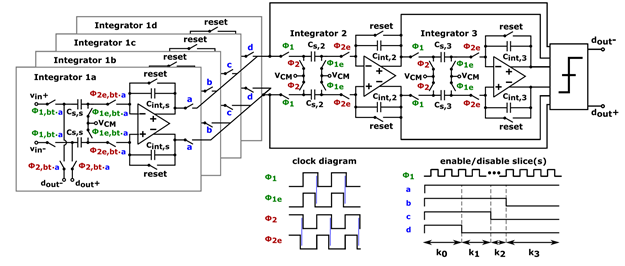

由上图可见,随着 k 的增加,数字滤波部分对 dn[k] 的权重是变小的,因此可以考虑在在后面若干个周期放松对于 ADC 的噪声等性能的要求,以降低功耗而不显著影响最终的性能,这样的结构如下图所示,即将第一级拆分并动态的关闭的方法。