10月份的 JSSC,主要挑了下面的论文:

A 72.9-dB SNDR 20-MHz BW 2-2 Discrete-Time Resolution-Enhanced Sturdy MASH Delta–Sigma Modulator Using Source-Follower-Based Integrators

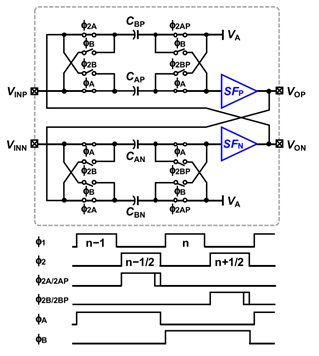

论文介绍了用源跟随器 (SF)实现的积分器的结构,如下图中所示:

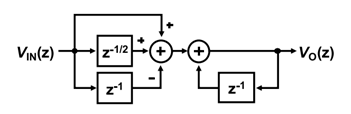

这种方法得到的积分器的 z 域特性如下图所示,可以看到他与理想积分器的差别主要在于图中前半部分多出来的求和项。在实际的 sigma-delta 环路的设计中,通过对第一个积分器采用合适的时序可以将其变为理想的半延迟的积分器,对第二个积分器则直接利用的这一额外的特性将环路中积分器的前馈部分直接包含进去。

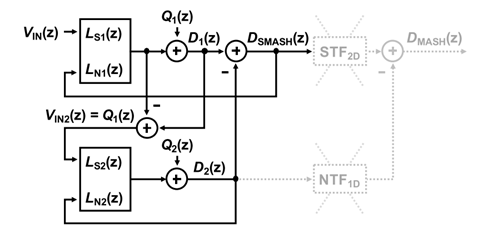

考虑到跟随器的非理想问题,系统采用了 sturdy-MASH 的结构,如下图所示

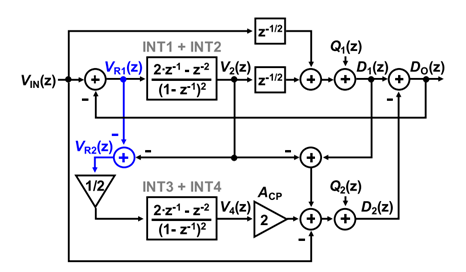

对比虚线部分的常规 MASH 结构,Sturdy MASH 结构不再要求电路 NTF 与数字部分的 matching,但存在的问题是仍会有第一级的量化噪声出现在输出。这一问题,主要是考虑第二级的 STF 的影响,论文最终提出的结构如下图: