8月份的 JSSC, 主要挑了下面两篇论文:

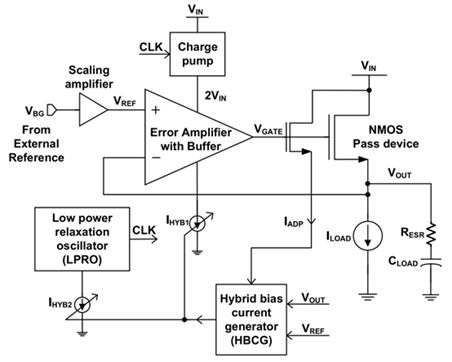

A 1.24 μA Quiescent Current NMOS Low Dropout Regulator With Integrated Low-Power Oscillator Driven Charge-Pump and Switched-Capacitor Pole Tracking Compensation

论文主要分析了 LDO 在空载下的静态功耗和瞬态响应速度的问题,并通过采用 Hybrid 电流偏置和在 EA 中的 fast pull-up/pull-down buffer的结构来加以改善,下图为电路原理示意:

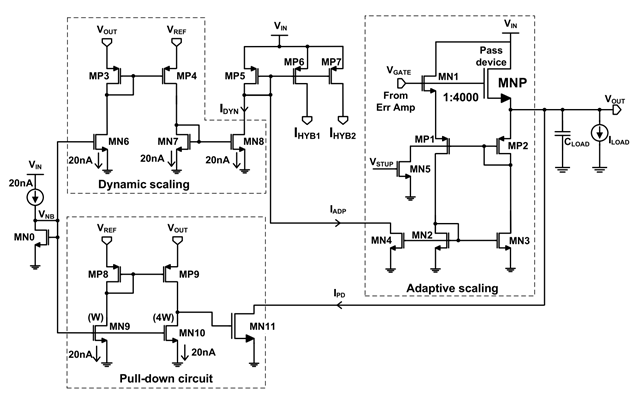

其中具体的 HBCG 电路如下,注意这里包含的三部分,分别是跟踪轻重负载的 Adaptive bias,改善 under-shoot 响应的 Dynamic scaling 电路和改善 over-shoot 响应的 Pull-down 电路。

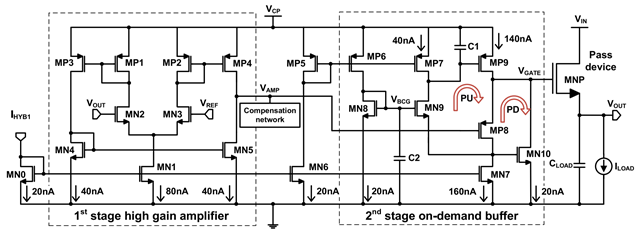

下图为具体的 EA 电路,需要注意这里的 buffer 级电路同时提供了 pull-up 和pull-down 的路径,同时这里的频率补偿网络采用了开关电容的方式实现大的电阻值,并通过开关频率的电流的关系来使得补偿的零点能够跟踪负载情况。

A 65-nm CMOS Low Dropout Regulator Featuring >60-dB PSRR Over 10-MHz Frequency Range and 100-mA Load Current Range

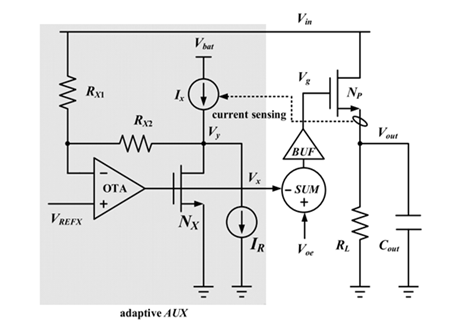

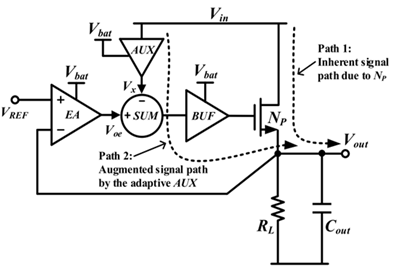

论文主要是通过采用 AUX 的运放来增加额外的前馈通路,从而将两个路径的输入电源 Vin 的信号相消,从而提高其 PSRR,如下图所示:

论文通过分析和具体参数的选择,提出当 AUX 提供的增益为 Np 的本征增益的倒数时,可以实现两路信号的相消,下图即为对应的 AUX 电路的原理示意。通过反馈电阻的选择,使得 Vy 和 Vin 的信号大小相同,因此 AUX 的增益 Vx/Vin=Vx/Vy,也即 Nx 的本征增益的倒数。同时考虑通过电流检测使 Nx 与 Np 有相同的电流密度,并通过 Vrefx 的选择使两个 MOS 管的 Vds 相同,从而使得 AUX 的提供的增益满足要求。