继续关于 Journal of Solid-State Circuits 的论文的纪录, 11月主要挑了下面两篇 paper:

An 80-mVpp Linear-Input Range, 1.6-G Input Impedance, Low-Power Chopper Amplifier for Closed-Loop Neural Recording That Is Tolerant to 650-mVpp Common-Mode Interference

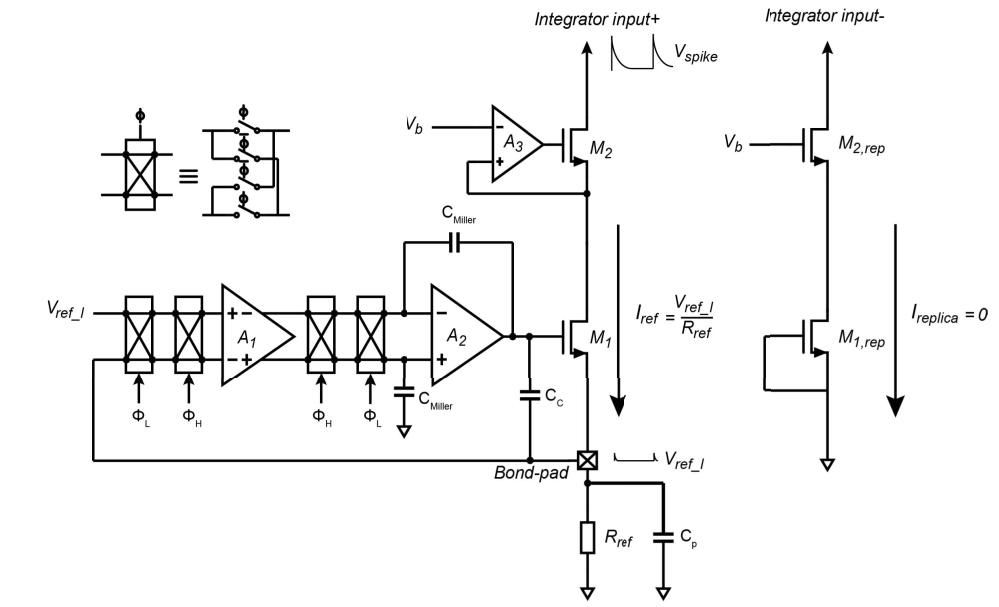

论文主要介绍的是在低压低功耗的条件下满足对动态范围、高输入阻抗和抗共模干扰能力的要求,下图所示为论文介绍的系统框图:

对于大的共模干扰的问题,论文主要是采用了对共模扰动前馈相消的 CM cancellation 电路,以解决低压低功耗设计的运放的有限共模范围的问题;对于系统的输入阻抗,主要是 chopper 工作模式下抽取电荷的问题,通过增加额外通路以输入 buffer 实现预充电的方式加以改善;最后电路中的大电阻以 duty-cycled resistor 来加以实现。

A Precision Capacitance-to-Digital Converter With 16.7-bit ENOB and 7.5-ppm/°C Thermal Drift

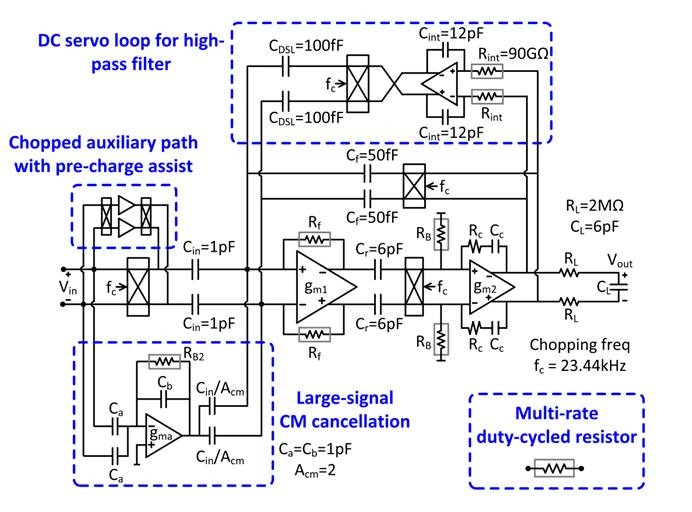

利用精确的 V2I 和开关电容的 charge-balanced incremental SDM 环路的结构,具体可见下图,这里需要注意的是在输入增加了 replica network 从而实现伪差分的结构以减小电荷注入等问题的影响。

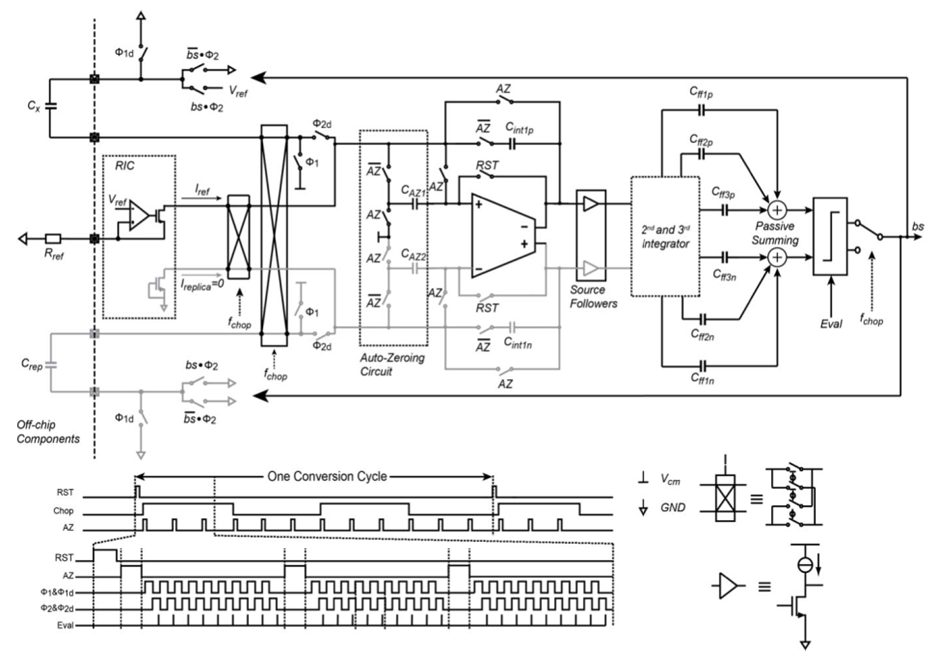

另一个需要注意的地方是在 V2I 的电路中采用的 nested-chopping 的方式(见下图),其中较高频率的 chopper 保证其对于 1/f noise 的抑制,而低频的 chopper 则用来消除由于高频 chopper 的 glitch 等导致的残余的 offset。