九月的 Journal of Solid-State Circuits, 找了下面这篇论文记录一下:

Analysis and Design of Continuous-Time Delta–Sigma Converters Incorporating Chopping

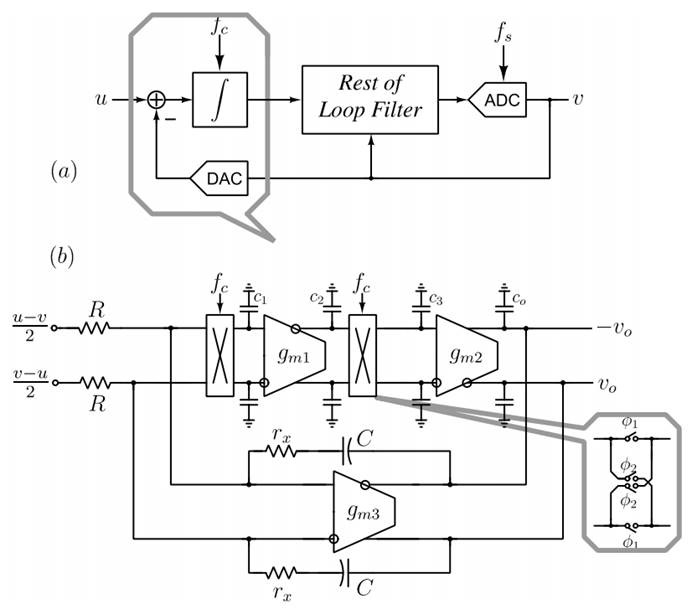

下图为所示的连续时间 SDM 的示意图,在第一个积分器中加入了 chopping 来改善 1/f noise 的问题,注意这里的积分器中的运放采用的是前馈方式的补偿方法。

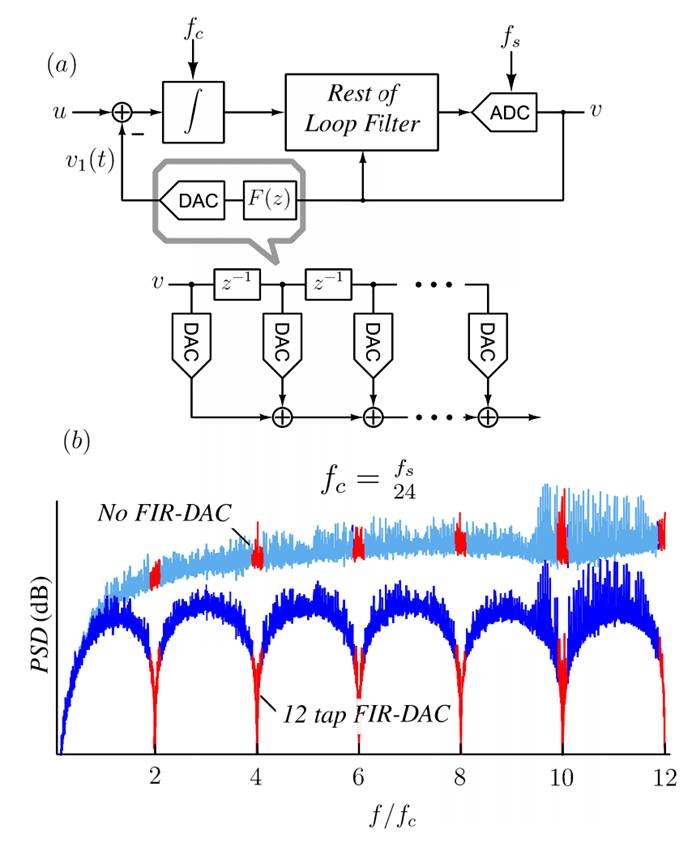

在 SDM 环路中加入 chopping 的潜在问题是:chopping 可能将高频的量化噪声折叠到带内,导致性能的下降。除了考虑选择适当的 chopping 频率来减小其影响外,论文主要是通过在反馈路径加入额外的 FIR 滤波以消除 Chopping 频率对高频噪声的混叠,如下图中所示。