继续记录一下四月份的 Journal of Solid-State Circuits 的论文, 挑了下面关于 temperture sensor 和 Incremental SDM ADC 的 paper 记录一下:

A BJT-Based Temperature-to-Digital Converter With ± 60 mK (3σ) Inaccuracy From -55 °C to +125 °C in 0.16 μm CMOS

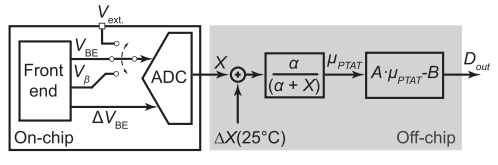

基于 BJT 的温度传感器的设计,基本上是利用三极管的 VBE 或者是 ΔVBE 电压与 VBG 电压的比值来确定芯片温度,下图所示即为基本的温度传感器的系统框图。

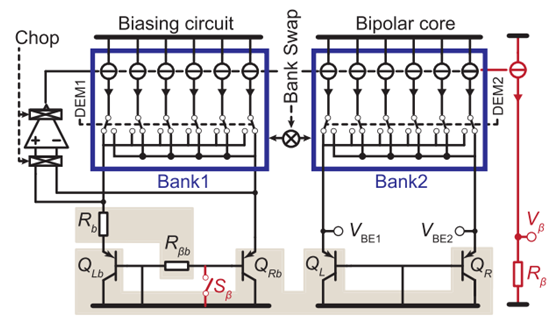

这里主要关注的还是前端的 BJT core 电路,具体可见下图。论文中采用了一系列方法来减少电路中的温度的非线性和工艺偏差带来的影响。具体包括:采用 PTAT 电流的偏置电路来减小 VBE 电压温度特性的非线性(曲率);选择合适的电流以减小电流水平对 BJT 的 β 的影响;利用 β 补偿电阻减小 β 的误差;利用 DEM 减小电流镜的误差,包括偏置电路和 core 部分的电流镜的动态交换。

A 16 b Multi-Step Incremental Analog-to-Digital Converter With Single-Opamp Multi-Slope Extended Counting

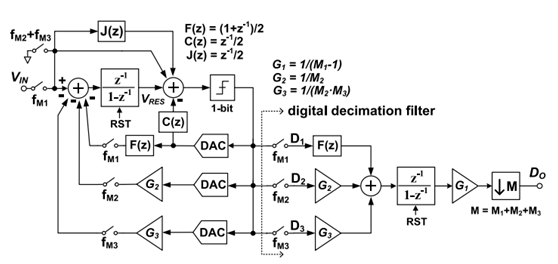

论文介绍的基本的 Incremental Sigma-Delta modulator ADC 的电路结构和时钟时序可见下图,主要是在一阶的 Incremental SDM 的工作时序之后,增加两段时间使电路以类似 Counting ADC 的模式工作。

可以注意电路处于 SDM 模式工作时的设置,这里采用了前馈方式的一阶 SDM 结构。通过在反馈路径增加 FIR 滤波的 F(z) 模块,减小了反馈输出的 step,因此可以放松对 OPAMP 的 slew-rate 的要求。同时为保证系统 NTF 不变,增加了 C(z) 的 local feedback 的路径,同时考虑到 C(z) 路径,为了保持原来系统前馈方式的优点,在输入增加了 J(z) 的前馈路径。