一月份的 Journal of Solid-State Circuits 主要是关于数字电路和存储器的内容, 简单的挑了下面关于 Digital LDO 的论文记录一下:

A 200-mA Digital Low Drop-Out Regulator With Coarse-Fine Dual Loop in Mobile Application Processor

与模拟方式工作的 LDO 不同, 数字方式的 LDO 通过控制 Power MOSFET 的数目来实现其功能, 由于数字 LDO 中的 Power MOSFET 工作在开关状态, 其尺寸远较模拟 LDO 电路中的小, 故在芯片面积上有较大优势. 考虑到数字 LDO 的输出电压的 ripple 和 PSR 问题, 数字 LDO 一般是用于给对电源波动较不敏感的数字电路供电.

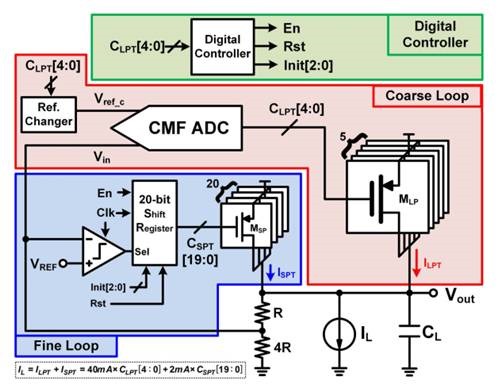

上图所示即为文章中具体提出的数字 LDO 电路的系统结构.

这里的电路采用了粗细两个环路的控制方法, 在粗调环路中利用了连续时间工作的电流镜方式的 Flash ADC (CMF ADC – Current Mirror Flash ADC) 控制电路输出大电流以此增强对负载电流的瞬态响应能力, 在细调环路中通过移位寄存器的控制电路提供小的输出电流, 减小输出电压的纹波, 同时提高电压调整的精度. 数字控制部分则提供对两个环路的控制以实现电路不同工作模式的切换.

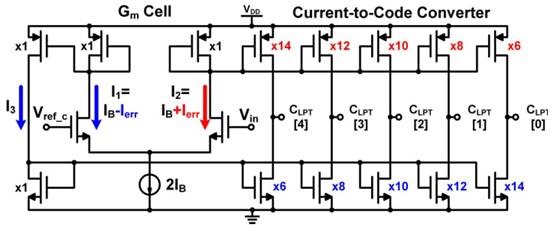

具体的 CMF ADC 的结构可见下图,通过这样的电流镜倍数的设计,可以使得电路中的 IB 与 Ierr 在不同比值关系时, CLPT[4:0] 有不同的输出, 从而实现 ADC 的功能.