在这里把看的有关 jitter 的内容整理一下:

Jitter is the undesired deviation from true periodicity of an assumed periodic signal in electronics and telecommunications, often in relation to a reference clock source. — from wikipedia

通信系统中的 Jitter

在文献【1】中提到,‘timing variations’可以分为两类:

- Wander: Timing variations that occur slowly

- Jitter: timing variations that occur more rapidly

两者之间一般以 10 Hz 为分界。

一般通信系统中的 Jitter 的类型可以按下图来划分,总的抖动 total jitter (TJ) 可以分为随机抖动 random jitter (RJ) 和确定性抖动 deterministic jitter (DJ) 两类.

Deterministic jitter 是可以重复和预测的,因此其峰峰值是受限的。

1. Periodic jitter 周期性抖动

主要指的是以周期性重复的特性出现的抖动(Jitter that repeats in a cyclic fashion),由于周期信号可展开为正弦的傅里叶级数,故此类 jitter 也称为 sinusoidal jitter.

(上图中 PJ 的概率密度 PDF,最大的概率出现在正负最大偏移处。对此的理解:对正弦波形的 jitter, 考虑其斜率在正弦信号峰值(Ymax)处最小,在0值时最大,当 x 轴区等间隔时,Y 最大时处出现的点更多,即概率密度在 Ymax 处最大,Y=0 时最小)

注意:这里的 Periodic Jitter 不同于后面的 Period-jitter !

2. Data-Dependent Jitter (DDJ) 数据相关抖动

与数据流中比特顺序相关的抖动,也称为符号间干扰(ISI:Inter-Symbol Interference)

(上图中 DDJ 的 PDF 的直方图中仅包含若干个脉冲. 可以理解为 ISI jitter 主要由之前的若干个比特的顺序来确定)

3. Duty-Cycle Dependent Jitter 占空比相关抖动,主要来源于:

a. 上升、下降沿的不同转换速率.

b. 判决阈值与理想值的差异.

(可以看到 DCD jitter 的直方图中 impulse 分为两组,这主要来源上升下降两个区域)

与 Deterministic jitter 不同,Random jitter 一般只能用统计特性来描述,这里我们主要分析 PLL 系统中的 noise 引入的 jitter.

PLL 系统中的 jitter

文献【2】和文献【3】中提到,在 PLL 系统中主要有两类模块,分别是 driven block(如 PFD,CP,divider 等)和autonomous block(如 OSC 和 VCO),他们对应不同的 jitter 的特性.

- Driven blocks:对应的是 synchronous jitter (或 PM jitter.),输入和输出事件的延迟时间的随机扰动

- Autonomous blocks: 对应的是 accumulating jitter (或 FM jitter),当前输出的跳变的与之前输出的跳变时刻的随机扰动

具体的 Jitter 的划分

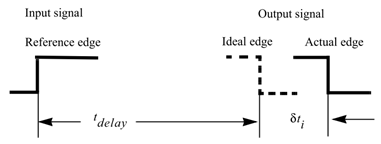

1. Edge-to-Edge Jitter (也叫 absolute jitter 或 aperture jitter)

由于其需要与理想的输入信号对比,主要是针对 driven systems.

2. Period jitter (Cycle Jitter) 周期抖动

单个时钟周期与理想周期(或平均周期)的扰动

3. Long-Term Jitter (K-Cycle jitter or K-Period Jitter)

K-period jitter 可以和 period jitter 关联起来,

- 对synchronous jitter: 由于k-period jitter 只与最初和最后时刻的输出和输入 delay 相关,故

- 对accumulating jitter: 考虑由 K-period jitter 的定义和 jitter 累积的特性,可以分析得到:

4. Cycle-to-Cycle Jitter (或 Adjacent Period Jitter)

相邻时钟周期之间的 short-term variation

上面提到的 osc 的 Long-term jitter 的累积特性,文献【4】中也给出了相应的说明,如下图所示:

左图为 VCO 的 jitter 特性,右图为 PLL 的 jitter 特性。实际若考虑 flicker noise 的作用,VCO 的 jitter 特性进一步可示于下图(文献【5】):

这里斜率的差异(由0.5向1的变化)主要来源于 jitter 的相关性,一般考虑热噪声的 jitter 是不相关的(平方和),而flicker noise 的 jitter 是相关的(直接相加)。

另外,若考虑 PLL 输入的 Reference clock 的 jitter,PLL 的 jitter 特性应为如下(文献【2】):

由 Phase-Noise 计算 Jitter

在IEEE标准(文献【6】)中,关于相位噪声等的定义:

Phase fluctuations Ф(t): Instantaneous phase departure from a nominal phase.

Phase spectrum SФ(f): One-sided spectral density of the phase fluctuations.

Phase noise L(f): One-half of the phase spectrum SФ(f),

传统上,相位噪声也有下式的定义,

并且定义有 Phase-Jitter:

从 SФ(f) 的意义来看,它所对应的是 absolute jitter

对 Period-Jitter (Cycle-Jitter),有类似的表述:

同样,对 Long-Term jitter (K-Cycle jitter):

(在文献【7】中有提到关于 TIE(Time Interval Error) 与相位噪声的关系,与 long-term jitter 类似)

关于积分中的 sin2 项的理解,可以参考文献【8】,基本上是考虑 Period-Jitter 对 absolute jitter 在离散域的一阶差分(first difference),z 域变换求幅度响应从而得到 sin2 项的 weighting。

类似的,关于 CyCle-to-Cycle jitter,也有:

上面的积分皆是由0到无穷,实际的积分常取下限频率 fL 和上限频率 fH (文献【9】),一般有提到下限频率选为10Hz (之前提到的 jitter 和 wander 的界限),上限频率一般由系统带宽来确定,也有提到选取为载波频率的一半或载波频率本身。

Reference:

【1】Tektronix: ‘Understanding and Characterizing Timing Jitter’

【2】Ken Kundert, ‘Modeling and Simulation of Jitter in PLL Frequency Synthesizers’

【3】Cadence Application Note: ‘Jitter Measurements Using SpectreRF Application Note’

【4】John A. McNeill, ‘Jitter in Ring Oscillators’, IEEE JSSC Vol. 32, No. 6, June 1997

【5】Rick Poore, ‘Phase Noise and Jitter’

【6】‘IEEE Standard Definitions of Physical Quantities for Fundamental Frequency and Time Metrology—Random Instabilities’ — IEEE Std 1139™-2008

【7】Scott W. Wedge, ‘Predicting PLL Phase Noise & Jitter with HspiceRF’

【8】David C. Lee, ‘Analysis of Jitter in Phase-Locked Loops’, IEEE Transactions on Circuits and Systems – II: Analog and Digital Signal Processing, Vol. 49, No. 11, Nov 2002

【9】Silicon Laboratories Application Note: ‘Estimating Period Jitter From Phase Noise’

Pingback引用通告: 关于 phase-noise 积分到 jitter 的理解 | Return To Innocence

一开始的jitter的图片掉了。

我这里看没问题的