继续关于 Journal of Solid-State Circuits 的论文的纪录, 三月份主要挑了下面的 paper:

A Low-Jitter Ring-Oscillator Phase-Locked LoopUsing Feedforward Noise Cancellation Witha Sub-Sampling Phase Detector

下图所示为常见的 CP-PLL 和论文中提到的 SSPD-PLL 的系统框图,以及两种结构中各个电路模块对的系统的相位噪声的贡献的曲线。

继续关于 Journal of Solid-State Circuits 的论文的纪录, 三月份主要挑了下面的 paper:

下图所示为常见的 CP-PLL 和论文中提到的 SSPD-PLL 的系统框图,以及两种结构中各个电路模块对的系统的相位噪声的贡献的曲线。

二月份的 Journal of Solid-State Circuits 论文, 简单的找了下面这篇记录一下:

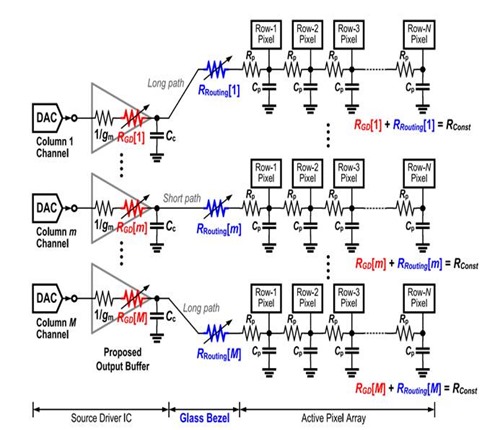

这里主要介绍的是利用在输入差分对加入源极退化电阻来补偿连线电阻的失配问题,基本的原理可见下图.

继续阅读

新一年的开篇,重新出发,这月的 JSSC 主要挑了下面这篇 paper:

这里主要是利用 Current Conveyor 的阻抗变换或者说 buffer 的作用以减少 sensor 中大的寄生电容的影响,同时对相邻的信号做差得到类似差分的结构以避免所谓的 baseline 信号导致的饱和的问题。

基本的系统结构可见下图:

继续关于 Journal of Solid-State Circuits 的论文的纪录, 11月主要挑了下面两篇 paper:

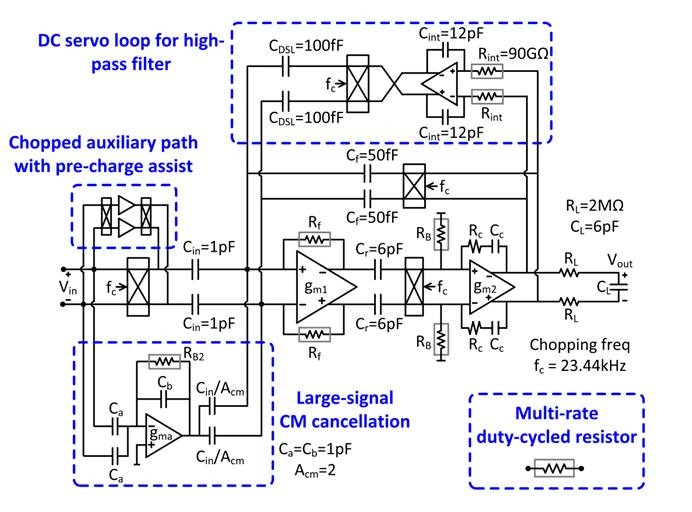

论文主要介绍的是在低压低功耗的条件下满足对动态范围、高输入阻抗和抗共模干扰能力的要求,下图所示为论文介绍的系统框图:

继续阅读

十月的 Journal of Solid-State Circuits, 主要找了下面的论文来简单记录一下:

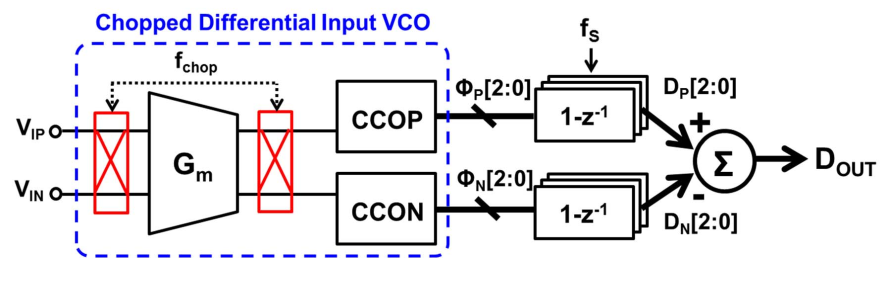

利用 VCO 实现的开环 CT-DSM, 直接由逻辑电路实现的 1-z-1 结构,如下所示:

继续阅读