关于PFD (鉴频鉴相器)的模型,一般在 Matlab 的 simulink 环境下比较容易实现,因为搭建 PFD 主要的模块都能在 simulink 的库中找到,直接按照电路一样搭建就可以了。在这里,我们主要关心的是基于 Verilog-A 的方法的实现, 以希望在之后的电路设计中方便实现的模型和实际电路的切换。

继续阅读

分类目录归档:专业|IC-Design

JSSC 2011-10 笔记

10月份的JSSC, 简单列一下觉得可以了解的内容:

Ultrahigh-Speed Low-Power DACs Using InP HBTs for Beyond-100-Gb/s/ch Optical Transmission Systems

在电路设计上,可以看看里面R-2R的current-steering DAC和 timing alignment的结构

Digitally Assisted IIP2 Calibration for CMOS Direct-Conversion Receivers

在接收机中使用数字辅助的自校准技术来改善IIP2的方法

关于 jitter 的小结

在这里把看的有关 jitter 的内容整理一下:

Jitter is the undesired deviation from true periodicity of an assumed periodic signal in electronics and telecommunications, often in relation to a reference clock source. — from wikipedia

通信系统中的 Jitter

在文献【1】中提到,‘timing variations’可以分为两类:

- Wander: Timing variations that occur slowly

- Jitter: timing variations that occur more rapidly

两者之间一般以 10 Hz 为分界。

Matlab 由时域仿真结果计算 jitter 的脚本

这里简单谈下由时域仿真结果计算 jitter 的方法。

关于如何计算 jitter, 这里的方法主要分为两步,首先在 Cadence 仿真中得到时钟信号过零点时刻的数据,然后利用 matlab 对此数据处理,从而得到 clock jitter 以及时钟周期的直方图(histogram)。

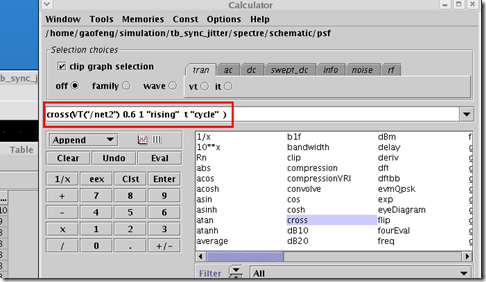

对于过零点时刻的获取,主要可以通过 calculator 中的 cross 函数对 spectre 时域仿真的时钟信号的处理来得到,如下图中所示。

关于 PLL 相位模型和环路参数

关于 PLL 相位域分析,有很多书中都有介绍,这里做一些小结

下面电路是利用 Cadence 中的基本元件搭建的 PLL 相位域模型

具体来说,这里的 PFD+CP 利用 VCCS 实现, LPF 直接电阻电容搭建, VCO 利用 VCCS 对单位电容充电实现频率到相位的积分,DIV 利用 VCVS 实现.

继续阅读

JSSC 2011-9 笔记

9月份的JSSC, 简单列一下觉得可以了解的内容:

Transmitter Linearization by Beamforming

结合beamforming和linearization的方法,减少PA数量,避免片上变压器的损耗,主要是发射机系统结构上的改进

A 0.46-mm2 4-dB NF Unified Receiver Front-End for Full-Band Mobile TV in 65-nm CMOS

利用 gain-boosting current-balancing balun-LNA ,current-reuse mixer-low-pass-filter 和 direct injection-locked 4-/8-phase LO generator 来提升性能,减小功耗和面积