三月的 Journal of Solid-State Circuits, 主要找了下面关于 Charge-Pump Converter 的论文来简单记录一下:

A 36-V 49% Efficient Hybrid Charge Pump in Nanometer-Scale Bulk CMOS Technology

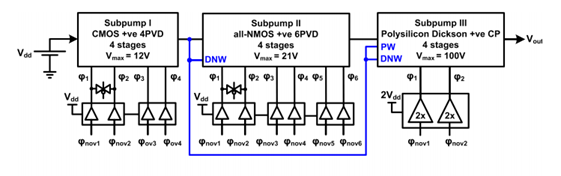

论文主要是介绍了基于耐压和效率的考虑而采用的三级混合结构的电荷泵电路,具体如下图所示。在 Charge-Pump 的第一级中采用了改进的 Cross-Coupled CMOS 电荷泵,主要是考虑到此时的电压仍在衬底耐压范围内,而对于后面两级电路,由于要求的电压较高因此电荷泵的第二级采用将MOSFET 的 DNW 单独接中间电位得到两个反偏的 PN 结串接来提升器件耐压,同样在第三级中利用多晶 P-I-N 结构来提升耐压。