继续之前关于 ESD 的内容:ESD 防护的基本目的在于:对大的 ESD 电流提供低阻泄放通路以避免热损坏,同时将芯片 pin 脚上电压钳位到安全电压防止介电击穿。

这里列举一下集成电路中常见的 ESD 保护器件和结构,具体更多的内容建议参考 ‘ Basic ESD and I/O Design ‘ 一书,感觉里面对 ESD 保护器件的叙述还是很全的

集成电路中常见的 ESD 保护器件和结构

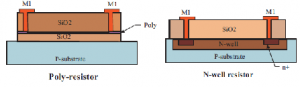

1.电阻

N 阱电阻与衬底接触,便于散热,一般利用 N-well 电阻作高 ESD 的限流电阻,而多晶电阻散热较差但其寄生较小,在低 ESD 时也有采用

当 N-well 电阻和 NMOS 接在一起做 ESD 保护时,需注意在 NMOS 雪崩时不会使N阱电阻热击穿

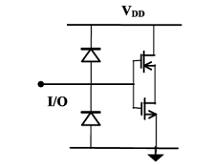

2. 二极管 diode

正向导通的 diode 能通过大的电流瞬态,但其问题在于较低的开启电压(~0.65V)的限制;多个diode 串接或可解决,但是其串联电阻变大,减小了电流泄放能力

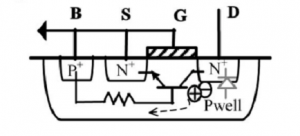

3. 栅接地 NMOS (GGNMOS)

当正向 ESD 电压加到 IO pin上,NMOS 的漏-衬底的 p-n 结反偏直到发生雪崩击穿,产生的空穴流向衬底-地,使其电势 VB 上升,进而使得寄生的横向 NPN 的 BJT 开启,提供的低阻的 ESD 电流泄放通路,ESD 电流从 BJT 的集电极(nmos的漏)流向 BJT 的发射极(nmos的接到地的源极),从而减轻 nmos 漏极(接到 PAD)的 ESD 问题;当负的 ESD 瞬态时,寄生的二极管提供ESD电流通路

GGNMOS 的尺寸要足够大以满足大的 ESD电流 :multiple fingers结构–>仍有finger的非均一导通问题–> ballasting resistor 镇流电阻的方法->下面的 GCNMOS

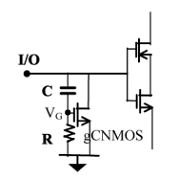

4. 栅耦合NMOS (GCNMOS)

为减轻 GGNMOS 的size的要求,利用电容耦合适当提升 NMOS 的栅电压,以增加衬底电流,加快横向 NPN 的 Vbe 的建立

RC 的选择注意避免对 NMOS 栅氧上有过大的电压

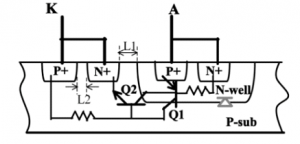

5. 可控硅整流器 SCR (Silicon-Controlled-Rectifiers)

*由于它的 deep snap-back I-V 特性,适合用于 ESD 保护中

当正向 ESD 电压 V(A,K) 加入时, 纵向的 PNP 管 Q1 的 BC 结击穿,产生的空穴电流流过寄生的衬底电阻,使横向 NPN 管 Q2 的 Vbe 上升,最终使 Q2 开启;为 ESD 电流提供低阻的泄放通路,同时SCR 较低的 holding voltage 也保证 IO pad 在安全电压内。反向的 ESD 电压时依靠二极管保护,其较低的电压在某些应用中不适用

*必须注意避免 SCR 可能的 latch-up 问题,

相对于 ESD NMOS, SCR 的较高的 ESD 击穿电压(40V, with latch-up time 1ns),在 ESD 保护电路作用之前,内部电路可能已被损坏 –> 故而有下面的结构:

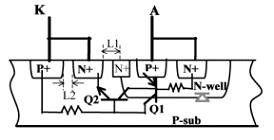

中等电压触发 SCR (Medium-Voltage-Triggered SCR)

在 n 阱边缘增加的 N+ 区域,减小雪崩击穿电压; 在较低的 ESD 电压下作用,25V for 0.35um CMOS

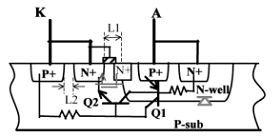

低电压触发 SCR (Low-Voltage-Triggered SCR)

这里增加的 GGNMOS 在 ESD 时首先发生雪崩击穿, 雪崩电压与 GGNMOS 的相近(10V左右)