开始慢慢恢复更新,补一下 2021年12月份的 JSSC 论文,主要看了这篇:

A Hybrid-Loop Structure and Interleaved Noise-Shaped Quantizer for a Robust 100-MHz BW an d 69-dB DR DSM

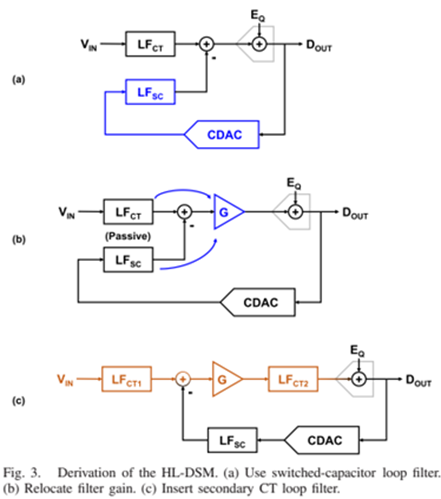

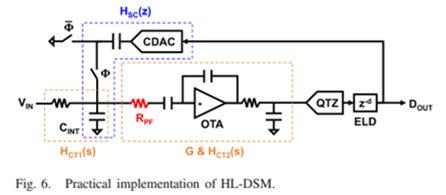

论文主要介绍了关于 hybrid-loop(HL) DSM 的结构: 其中的前馈路径使用 CT filter,保持了 CT-SDM 的好处(抗混叠,输入阻抗等) ; 反馈路径中使用 DT filter, 改善了 PVT,jitter, ISI 等问题。

下图中可以看到,通过把增益放在summing 节点之后,可以减小 summing 节点看到的幅度,避免放大器饱和;在增益后加入第二个 CT filter 则主要是为了减小summing 放大器的噪声的问题。