八月的 JSSC,主要看了下面的论文:

A 5.6 μA Wide Bandwidth, High Power Supply Rejection Linear Low-Dropout Regulator With 68 dB of PSR Up To 2 MHz

论文主要是考虑 LDO 的 PSR 的问题,通过将电源的 ripple 前馈到输出 PMOS 的 gate, 使其成为类似共模的信号,从而提高最后输出的 PSR。

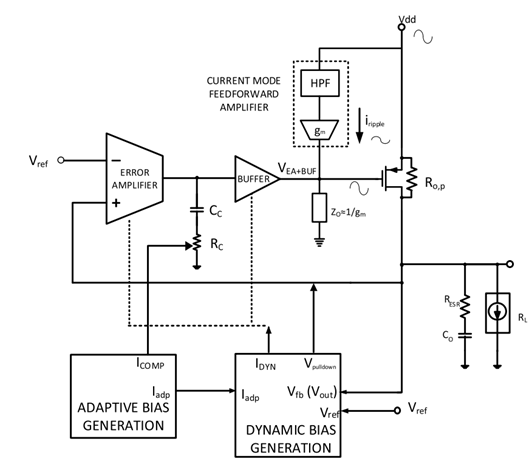

下图所示为论文介绍的 LDO 的结构,这里主要是多了一个电流模方式的前馈通路,通过论文的分析,为了去除电源的 ripple 的影响,需要使得前馈的 gm 与 buffer 级的 gm 一致。

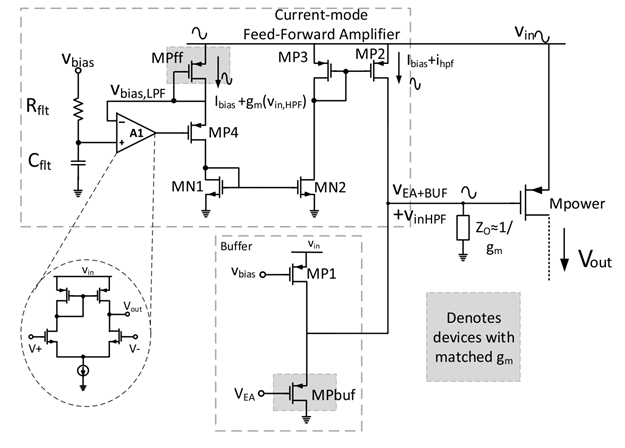

具体的前馈电路如下图所示,Vbias 通过大的 RC 滤波,并通过 A1 使 Mpff 的 gate 近似虚地,从而可将电源的 ripple 转为电流信号。前馈的 gm 与 buffer 级的 gm 的一致的要求,这里主要通过相同的 Vbias 和 两个 PMOS 的匹配来加以实现。

一般也没看到做这么低的

大大,这篇文章的相位裕度好小啊,而且带内几乎到0°了。这在工程中实用吗?