6月份的 JSSC,主要看了下面的论文:

A Second-Order Noise-Shaping SAR ADC With Passive Integrator and Tri-Level Voting

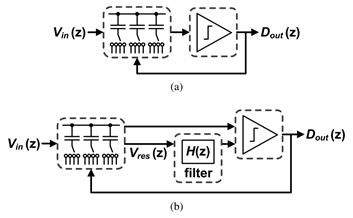

如下图所示,这里的 Noise-Shaping SAR ADC 与一般的 SAR ADC 的差别主要在于将将 SAR 工作后的 Vres 取出经过滤波 H(z) 后加入下次的 SAR 工作,以此来实现量化噪声的整型。

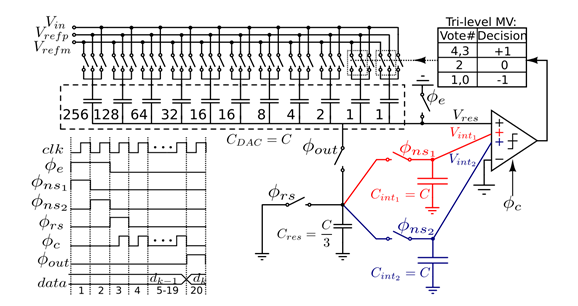

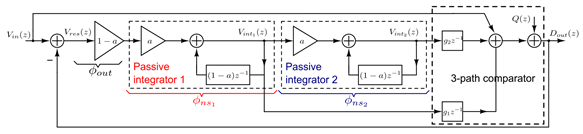

下图是具体的示意,每次 SAR 逻辑完成之后,将 Vres 存到 Cres 电容上,随后 Cres 相继接到 Cint1 和 Cint2,完成等效的积分的功能,相应的电压在量化器相加,等效的 SDM 环路的结构也在图中绘出。