之前写过cascode补偿的一些内容,最近看到一些相关的讨论,这里试着从另外的角度来做些分析。

众所周知的,对基本的 miller compensation (米勒补偿)的两级运放,由于存在前馈通路,会引入一个右半平面的的零点,从而使得频率响应的稳定性变差。一般除了常用的加 nulling resistor(调零电阻)的方法之外,cascode compensation 也是常用的消除 miller 补偿的右半平面零点的方法。

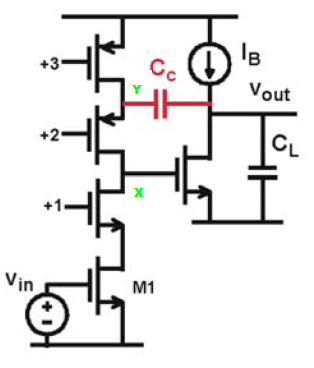

下图所示是就一个利用 cascode 补偿的电路

,

,

电路中,通过将补偿电容Cc的一端由X点移到Y点,将补偿从一般的miller补偿变为cascode补偿,并利用cascode将由X点经由电容Cc到输出的前馈通路截断。

为理解cascode的所谓‘截断’作用,我们可以考虑一下由X点到Y点的小信号增益,即考虑从cascode管的漏极加入电压信号,看其源极的电压大小。

在小信号下,简单将其源极接的mosfet认为是一大小为ro电阻,同时cascode管的电阻rds亦为ro,我们可以分析其中电流,有:Vy/ro=-gm*Vy+(Vx-Vy)/ro, 简化可得Vy/Vx=1/(2+gm*ro)

可以看到其源极的小信号电压被衰减为漏极信号的1/(2+gm*ro),从而实现了所谓的‘截断’的功能,或者说将此右半平面零点推到很高频率。

实际上,cascode补偿的一个优点是其对电源抑制比(PSRR)频响的改善:对一般的miller补偿,miller电容在交流下‘短接’,从而使第二级的共源放大管在ac下漏源短接(diode连接),考虑到其偏置电流不变,这样电源上的电压直接耦合到漏端输出,显然一定频率下PSRR性能变差。通过采用cascode补偿地方法可以改善这一问题,Ahuja最早在83年对cascode补偿的论文(’An improved frequency compensation technique for CMOS operational amplifers’)有关于此的叙述(因此,cascode补偿有时也被称为Ahuja-compensation)。

当然,在Ahuja最初的结构中,并没有将cascode并入到主电路而是额外加了一级,这样他的结构中的非主极点对输出负载电容的依赖减小了,从而在负载电容较大时仍能满足稳定性的要求。但是,现在将cascode并入主电路之后(如实际的folded-cascode),频响的问题会变复杂,次极点会变为一对复极点,从而需考虑避免他在频响中带来的 peaking ( 即使已在单位增益带宽外 ), 关于具体的分析可以参见 jssc 84 年的论文 ‘ Design Technique for Cascode CMOS Op Amps with Improved PSRR and Common-Mode Input Range ’.

你好,请问最后一段说到的 “并没有将cascode并入到主电路而是额外加了一级,这样他的结构中的非主极点对输出负载电容的依赖减小了” 这句话没太理解 在哪篇文章有?

难道不是从Cc前馈过来的信号Vy被放大了2+gm*ro倍?

看 cascode 部分,vx 到 vy 信号被衰减

这一段的逻辑可能有点问题,实际上信号的方向应该是vy到vx,理解为由 cascode补偿改为miller补偿后,feed-forward电流增大(2+gm*r0)倍。虽说反过来说从数学上讲没问题,但是信号方向可能有待商榷。

老师,我在仿真cascode补偿的时候,在GBW处一直有一个peak,导致Gain-margin不够,有什么方法能够去除这个peak吗?我看是一个右半平面的零点导致的,可是即使增加第二级的跨导,对零点还是几乎没什么影响,还有您听过米勒倍增补偿吗?有这方面的论文推荐吗?

可当不起老师,gain-peaking 应该还是共轭极点的问题吧,上面最后提到的论文里面有比较详细的推导。米勒倍增补偿是指电容倍增的方法?印象里面有一些 LDO 的论文谈到过,好像 Rincon-Mora 写过几篇。

好的,谢谢您,我去找找看

对于文中的图,请问在补偿时,如果在M1 的D极也连接一个电容到Vout,会对增益的peak有消除或者减弱的作用么、、

Sansen 书里提了一句,CC 接到下面的 cascode 会稍微好点

这个看到了..想问如果两个一起接着的话,就是效果的折中么~谢谢

还有,,不知道您有没有看过2002 年的FAST-SETTLING CMOS TWO-STAGE OPERATIONAL TRANSCONDUCTANCE AMPLIFIERS AND THEIR SYSTEMATIC DESIGN这篇论文。。如果把Cc接在上面的位置似乎好一点,只存在一个零点。。

‘Design Techniques for Cascoded CMOS OpAmps with Improved PSRR and Common-Mode Input Range’ 这篇 paper 后面的分析看 gain-peaking 还是共轭极点的影响而不是 zero 的作用,至于是不是拆成两个电容,可以看看这篇 paper: ‘Hybrid Cascode Compensation for Two-stage CMOS Opamps’