在电路设计中,常见到利用 MOS 电容做去耦电容(也有利用来做miller补偿的电容),因此对 mosfet 的 c-v 特性曲线有必要进行确认。

关于具体的 c-v 曲线的仿真方法,首先可以从电容的定义(或者说特性)来确定测试方法,这也是 ee240 里面提到的仿真方法。

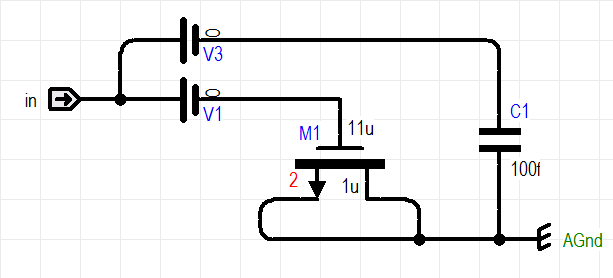

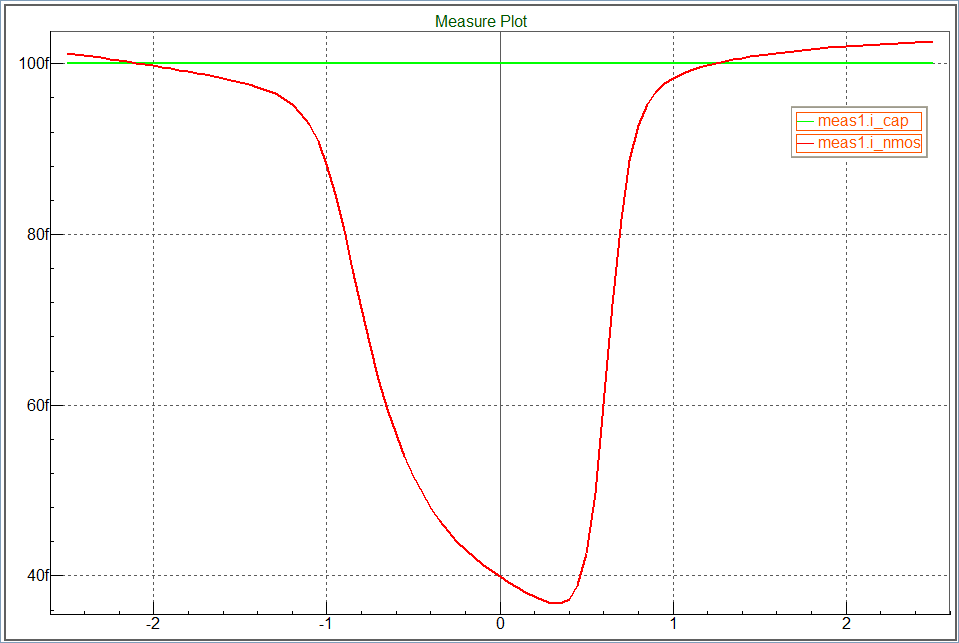

下图是实现 MOSFET C-V 曲线的仿真的具体电路(图中加上的电容 C1 仅为方便比较)

在输入节点加入一个电压,做 AC 分析,同时扫描其 DC 值,考虑电容特性:ac 下 i/v=2*pi*f*C;如果令交流电压 v ac=1,选择频率 2*pi*f=1,这时得到的交流电流大小就是电容值,相应的 smart-spice 脚本如下:

vin in 0 ac 1

.ac DEC 10 '0.05/3.14159265' '0.5/3.14159265' sweep vin -2.5 2.5 0.05

.measure ac i_nmos find i(V1) at '0.5/3.14159265'

.measure ac i_cap find i(V3) at '0.5/3.14159265'

注:AC 分析似乎没法对单独的频率点进行分析,所以上面还是对一段频率扫描,最后只取了我们所要的频率点的结果

在 hspice 文档里面提到了的另外的一种方法, 就是直接对上图的 vin 做 dc 扫描, 利用 option dccap 使 spice 在 DC 分析时计算栅节点的所有电容, 得到的结果与上面 ac 分析的方法也是一致的, 其具体的 samrt-spice 脚本如下:

.option dccap

.dc vin -2.5 2.5 0.05

.probe @M1[cgtot]

sweep扫描的是频率吧 为什么我输出图形横坐标为频率呀

仔细看 sweep 的是vin

你好 我想做铁电电容模型的C-V测试 初接触Hspice 不知道如何写出网表 求教

第一个方法试的时候发现测出来偏大,后来发现把实部也算进去了。

这里分享一下经验教训,.measure ac i_nmos find ii(V1) at ‘0.5/3.14159265’

如何才能知道mos电容的等效串联电阻呢,也就是沟道电阻哦?

电容串联电阻,ac分析看实部