这里把利用 Verilog-A 模型实现压控电容的方法记录一下

具体的 Verilog-A 模型描述:

// Verilog‐A model for Voltage Controlled Capacitor

`include “constants.vams ”

`include “disciplines.vams”

module vccap(p,n,vp,vn);

inout p,n; input vp,vn;

electrical p,n,vp,vn;

parameter real c0=1p from (0:inf); //nominal capacitance for V(vp,vn)=0

parameter real c1=0.1p from [0:inf); // v2c coefficience

real q, ceff;

analog begin

ceff=c0+c1*V(vp,vn);

q=ceff*V(p,n);

I(p,n)<+ ddt(q)

end

endmodule在上面模型的描述中,实际上假设了电容的控制电压与电容的端电压无关,因此直接 C*V 得到电荷,实际上如果是非线性电容,或者说电容同时受到其端电压控制,则需要通过非线性电容对端电压积分才能得到对应的电荷。此时具体的描述方法可以参见 Modeling Varactors 这篇 paper 中 Ken Kundert 关于非线性电容的模型描述方法与电荷守恒问题的分析。

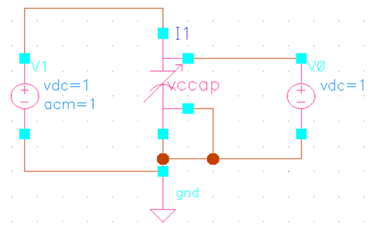

回到上面的 Verilog-A 模型,我们可以通过仿真来加以验证,下面是具体的 test-bench:

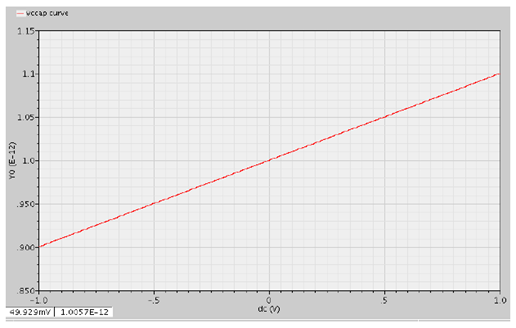

至于具体的仿真方法,仍然是通过 ac 分析得到交流电流,进而得到等效的电容,具体得到的电容随控制电压的变化曲线如下:

可以看到在电压从 -1 到 1 变化时,电容变化为 0.9pF 到 1.1pF,对照之前的电容 Verilog-A 描述中的参数,可以看到模型工作正常

我知道了,orcad和pspice结合应该不能仿verilog-A模型,抱歉打扰了(T_T)

您好,可不可以以请问一下具体用verilog-A建模然后导入模型生成压控电容的过程呀?因为我看这个背景图感觉是用orcad画的,我很想知道orcad里怎么使用verilog-A模型。我在论文里看到类似的操作,但上网查过很多次都没有结果。您的博客是我目前唯一找到的有这种类型的操作(T_T)