这里把利用 verilog-a 模型实现迟滞比较器的方法记录一下。

关于迟滞比较器,在实际的模型的构建中主要是考虑利用 @cross 语句来确定不同的翻转点, 这里需要注意的是初态的设置以保证翻转的触发。具体的 verilog-a model 描述如下

// VerilogA for comparator with hysteresis

`include "constants.vams"

`include "disciplines.vams"

module comparator (out,inp,inn);

inout inp, inn;

output out;

electrical inp, inn, out;

parameter real offset = 0; // Offset voltage (V)

parameter real hyst = 100m from [0:inf); // Hysteresis (V)

parameter real thrlo = offset - 0.5*hyst; // Lower threshold voltage (V)

parameter real thrhi = offset + 0.5*hyst; // Upper threshold voltage (V)

parameter real vh=3.3;

parameter real vl=0;

parameter real ttol = 2p;

parameter real td=20p;

parameter real tt=10p;

real n;

analog begin

@(initial_step) begin

if (V(inp,inn)>=offset) n=1;

else n=0 ;

end

@(cross(V(inp,inn)-thrhi, 1, ttol))

n = 1;

@(cross(V(inp,inn)-thrlo, -1, ttol))

n = 0;

V(out) <+ transition(n ? vh : vl, td, tt);

end

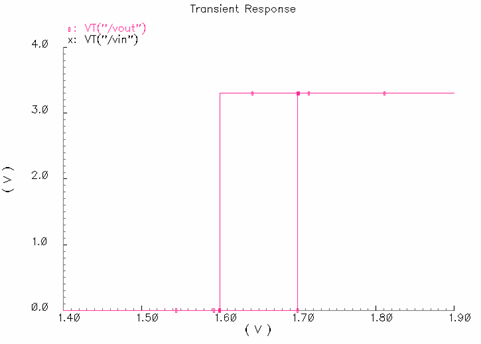

endmodule这里的主要问题是模型只能用于瞬态的分析,考虑到迟滞比较器的应用情况,上面的模型基本还是够用的。我们可以通过仿真来看下模型是否工作,对其做瞬态分析(输入信号的缓慢斜升/降),可以绘制得到下面的迟滞窗口,可见工作正常

请问可以给一个strong arm latch 的模型吗?

关注作者了。我这个小白找到了一个大神的博客呀!大神有没有什么交流群,让小弟我觐见一下

我想问下 您这个初始状态是怎么而设置的?还有仿真的时候是如何设置的呢?我参照这个写了一段程序,但是仿真结果总出不来,不知道是什么原因啊~

上面说的个初始状态那就是 model中的 @(initial_step) 部分。仿真的话,当时用的 cadence 版本里面的dc分析还没有迟滞分析的选项,所以用的是瞬态仿真,就是比较器一端接Vdc, 一端用Vpwl 做个先上升后下将的电压,最后在波形窗口里面把这个Vpwl作为x轴。

就是说 初始状态要设为“tran”,然后进行瞬态分析,是不?我做的dc分析出来结果始终为零。我再试试哈~O(∩_∩)O谢谢