打算抽空把模拟集成电路设计的基础知识清一遍,先从 MOSFET 的基本内容开始.

MOSFET 的体效应(body-effect,也叫衬底调制效应/衬偏效应),主要是来源于 MOS 管的 S-B(Source-Bulk)端之间的偏压对 MOSFET 阈值电压 vth 的影响:

以 NMOS 的晶体管为例,当晶体管的源端的电势高于体端电势时,源和体区的二极管反偏程度增加,栅下面的表面层中将有更多的空穴被吸引到衬底,使耗尽层中留下的不能移动的负离子增多,耗尽层宽度增加,耗尽层中的体电荷面密度 Qdep 也增加。而从一般的 MOSFET 的阈值电压的关系式中 Vth 与 Qdep 的关系(可以考率 Vth 为 MOS 栅电容提供电荷以对应另一侧耗尽区固定电荷的大小),可以看到阈值电压将升高。

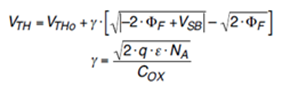

在考虑体效应之后,MOS 管的阈值电压可以写为:

其中 γ 称为体效应因子, 通常与具体工艺相关。

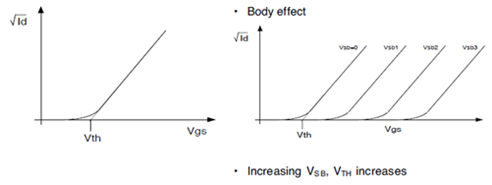

我们可以在下图直观的了解 VSB 对 Vth 的影响,随着 VSB 电压的增加,阈值电压相应的增大。

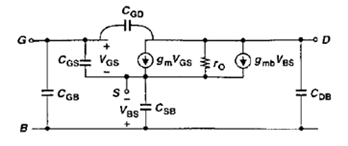

相应的, 由于体效应的存在, 在 MOSFET 的小信号模型中, 需要在 gm*VGS 的电流源旁并联一个大小为 gmb*VBS 的电流源

实际上,体效应也可看成在 MOSFET 中存在由体端电压控制的寄生的 JFET,若认为 MOSFET 的栅电压通过栅电容 Cox 控制沟道,则此 JFET 可以认为是通过耗尽区电容 CD 来控制沟道的导电能力。

对于 N 阱工艺,由于阱区的掺杂浓度一般高于衬底的掺杂浓度,考虑到体效应与杂质浓度成正比(也可认为 N-well 中有更大的耗尽层电容),因此 PMOS 相较 NMOS 有更显著的体效应。 一般可以将PMOS 的 N-well 和 S 端接一起以消除体效应时,但此时需要注意 N-well 到衬底的电容的影响(这一电容在模型中可能不会考虑,一般可以假设电容大小为0.1fF/um^2 ) 确定是否影响电路中的信号通路。

博主,麻烦问一下,2faiF是怎么算的啊?

衬底的费米势,和掺杂浓度相关,具体可以翻翻半导体器件物理之类

好的谢谢博主~